Fan, Zaiming (2016) Investigation on smart bi-directional inverter with quantitative reactive power compensation and interleaved DC/DC converter for micro-grid system. Doctoral thesis, University of Cumbria (awarded by Lancaster University).

Downloaded from: http://insight.cumbria.ac.uk/id/eprint/3326/

Usage of any items from the University of Cumbria's institutional repository 'Insight' must conform to the following fair usage guidelines.

Any item and its associated metadata held in the University of Cumbria's institutional repository Insight (unless stated otherwise on the metadata record) may be copied, displayed or performed, and stored in line with the JISC fair dealing guidelines (available <a href="here">here</a>) for educational and not-for-profit activities

#### provided that

- the authors, title and full bibliographic details of the item are cited clearly when any part of the work is referred to verbally or in the written form

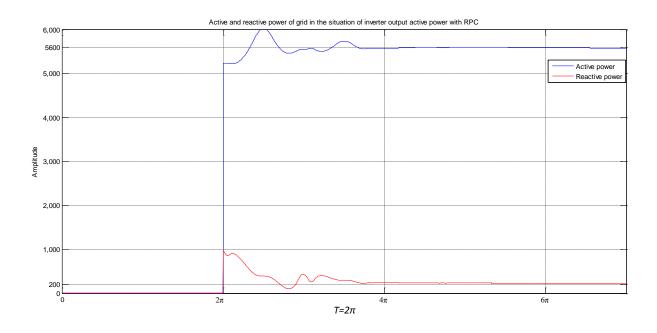

- a hyperlink/URL to the original Insight record of that item is included in any citations of the work

- the content is not changed in any way

- all files required for usage of the item are kept together with the main item file.

#### You may not

- sell any part of an item

- refer to any part of an item without citation

- amend any item or contextualise it in a way that will impugn the creator's reputation

- remove or alter the copyright statement on an item.

The full policy can be found here.

Alternatively contact the University of Cumbria Repository Editor by emailing <a href="mailto:insight@cumbria.ac.uk">insight@cumbria.ac.uk</a>.

# Investigation on Smart Bi-Directional Inverter with Quantitative Reactive Power Compensation and Interleaved DC/DC Converter for Micro-Grid System

by

**Zaiming Fan**

Thesis submitted for the degree of Doctor of Philosophy

of the

Lancaster University (University of Cumbria)

Department of Engineering

November 2016

All Glory be to God the Father Almighty.

Dedicated to my wife, my son and my parents.

Thanks for their support and trust.

### Acknowledgements

First of all, I am extremely happy to be a student of Professor Xiongwei Liu, who is my director of study. I am also rather grateful to his careful and generous guidance and help during my PhD study.

With great pleasure, I also express my gratitude to Professor Diane Cox, Sonia Mason and Sonia Barnes. They were always supporting and helping me at every stage of this work.

In particular, I would like to thank my friend Michael Peak and his wife Zhang Hui for their help. I also thank Dr. Elizabeth Tso, Dr. Mike Peak and Dr. Oyebanji Olusayo for their thorough proof-reading.

My thanks go to all my research office colleagues for a harmonious atmosphere.

Finally, I would like to thank the staff members of the University of Cumbria and Lancaster University for their support for my PhD study.

### **Abstract**

The PhD project aims to develop a smart grid-connected inverter (SGCI) for a micro-grid, which can be applied in a built environment such as a community, and associated power electronic DC/DC converters. The micro-grid generally includes distributed renewable power generators and battery storage.

The SGCI is a bi-directional DC/AC inverter for distributed generation with battery storage installed at its DC side. In one aspect, it is expected the DC/AC inverter functions as a controlled inverter that can deliver expected real power to the power grid with quantitative reactive power compensation (RPC). In other words, all the SGCIs in the community microgrid can share the reactive power of the whole community because a SGCI can quantify its active and reactive power output. It is also expected that the inverter can work in both ongrid and off-grid modes. In other words, the DC/AC inverter functions as a controlled rectifier with high quality power factor correction (PFC), which can deliver expected DC power from the AC power grid at unity power factor. With the above features, battery storage on the DC bus of the SGCI can be charged/discharged through a four-phase, interleaved, bi-directional, boost/buck DC/DC converter (IBDBBC) for distributed renewable power system, either wind or solar PV or hybrid wind/solar PV system. The IBDBBC can discharge power from a low voltage battery to a high voltage DC bus as the IBDBBC operates in boost mode, or it can also draw power from the DC bus to charge the battery as the IBDBBC operates in buck mode.

Based on MATLAB/Simulink, a mathematical model was developed for the grid-connected bi-directional DC/AC inverter that operates as a rectifier with PFC and as a grid-connected inverter (GCI) with expected real power output and quantitative RPC.

In a practical application, the sampling of input signal through AD converter usually has some noise due to common-mode interference; simulation results demonstrate that the second order

generalised integrator (SOGI) has great advantages to prevent interference. Therefore, SOGI can be utilised to construct a pair of orthogonal signals in a single-phase system to instantaneously split grid's active and reactive power to achieve RPC for local community loads. The methodology of the constructed the pair of orthogonal signals was also used to generate the required reference current for the DC/AC inverter when which operated as a single-phase rectifier with PFC.

Using three TI C2000 Solar Inverter DSK Boards, a small lab scale distributed power system was developed. In the lab distributed power system, the operating mode of the inverters could be switched between on-grid and off-grid through instruction from the control centre. The lab test outcomes demonstrate that each distributed power system unit worked properly under loss of power grid signal, simulating grid failure.

### **Abbreviations**

AC Alternating Current

AC/DC Alternating Current to Direct Current

AD Analogue to Digital

APLL Analogue PLL

CCS Code Composer Studio

CCM Continuous Conduction Mode

CPU Control Processor Unit

CSI Current Source Inverters

DCM Discontinuous Conduction Mode

DPLL Digital PLL

DSP Digital Signal Processor

DC Direction Current

DC/AC Direction Current to Alternating Current

DC/DC Direction Current to Direction Current

DG Distributed Generators

DSK Development Starter Kit

ESS Energy Storage System

EV Electrical Vehicle

FPWM Fuzzy PWM

FPU Floating-Point Unit

GCI Grid-Connected Inverter

GCIS Grid-Connected Inverter System

HCC Hysteresis Current Control

IBDBBC Interleaved Bi-directional Boost/Buck DC/DC Converter

IDE Integrated Development Environment

IGBT Insulated-Gate Bipolar Transistor

IO Input and Output

JTAG Joint Test Action Group

MPPT Maximum Power Point Tracking

PCC Point Common Coupling

PFC Power Factor Correction

PHS Pumped Hydroelectricity Storage

PI Proportional-Integral

PID Proportional-Integral-Derivative

PLL Phase-Locked Loop

PV Photovoltaic

PWM Pulse Width Modulation

RES Renewable Energy Source

RMS Root Mean Square

RPC Reactive Power Compensation

RTXD Real-time Exchange Data

SGCI Smart Grid-Connected Inverter

SDK Solar Inverter Development Kit

SFPLL Synchronous Frame PLL

SHEPWM Selective Harmonic Elimination PWM

SOGI Second Order Generalised Integrator

SOGIPLL Second Order Generalised Integrator PLL

SPLL Software PLL

SPWM Sinusoidal PWM

SSDG Small Scale Distributed Generators

STACOM Static Synchronous Compensator

SVPWM Space Vector Pulse Width Modulation

THD Total Harmonic Distortion

UPS Uninterruptible Power Supply

VAR Volt Amperes Reactive

VCO Voltage Controlled Oscillator

VFD Variable Frequency Drives

VSI Voltage Source Inverter

## **List of Figures**

| Figure 1- 1 Conventional RPC for solar PV power system                          | 2  |

|---------------------------------------------------------------------------------|----|

| Figure 1- 2 Proposed the diagram of small-scale GCIS                            | 4  |

| Figure 1- 3 Diagram of smart distributed micro-grid                             | 5  |

| Figure 1- 4 Topology of single-stage GCI                                        | 8  |

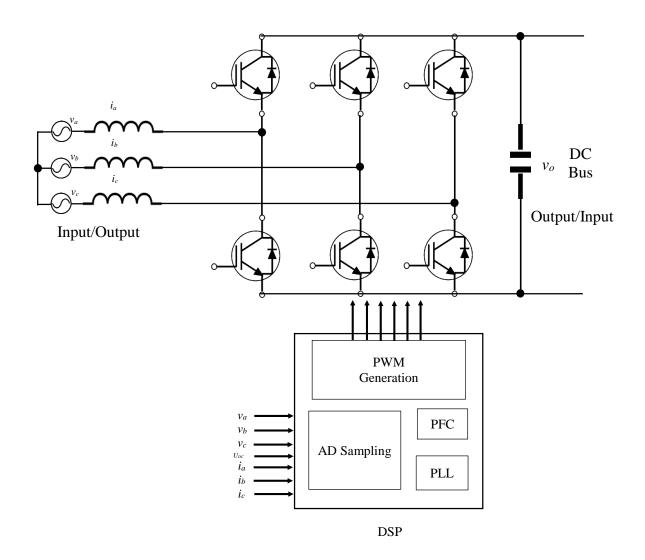

| Figure 2- 1 Structure of bi-directional three-phase rectifier/inverter topology | 13 |

| Figure 2- 2 The main board of C2000 <sup>TM</sup> SDK                           | 14 |

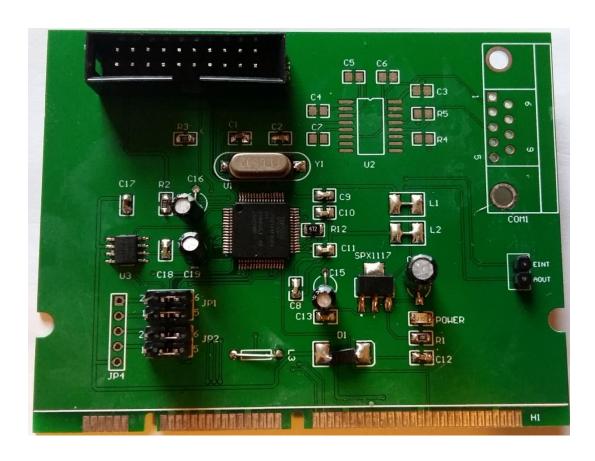

| Figure 2- 3 Control board of C2000 <sup>TM</sup> SDK                            | 14 |

| Figure 2- 4 Re-designed control board                                           | 15 |

| Figure 2- 5 Central control board                                               | 15 |

| Figure 2- 6 IGBT FF75R12RT4                                                     | 17 |

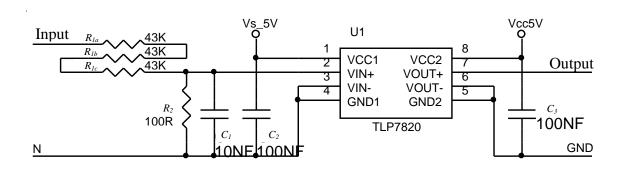

| Figure 2-7 Sampling circuit of input voltage                                    | 18 |

| Figure 2- 8 TLP7820 device                                                      | 18 |

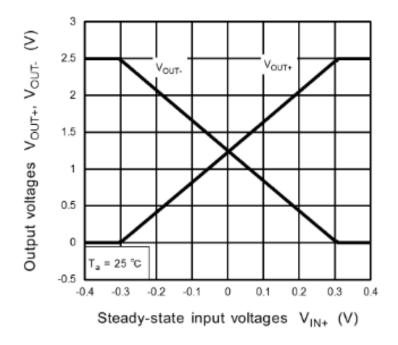

| Figure 2- 9 Linear relationship between input and output of TLP7820             | 19 |

| Figure 2- 10 Sampling Gain                                                      | 20 |

| Figure 3- 1 Diagram of generic PLL.                                             | 28 |

| Figure 3- 2 Linearised conventional SFPLL block diagram                         | 29 |

| Figure 3- 3 Open-loop system of SOGI                                            | 29 |

| Figure 3- 4 Close-loop system of SOGI                                           | 29 |

| Figure 3- 5 Step responses of a closed-loop SOGIPLL in continuous-time          | 31 |

| Figure 3- 6 Direct Form II structure for IIR filter                             | 34 |

| Figure 3- 7 Simulink model of SOGIPLL                                           | 36 |

| Figure 3- 8 Comparison between input with white noises and PLL output           | 36 |

| Figure 3- 9 Comparison of original input and PLL output                         | 37 |

| Figure 4- 1 Basic rectifier topologies with PFC                        | 40 |

|------------------------------------------------------------------------|----|

| Figure 4- 2 Topology of Vienna rectifier                               | 41 |

| Figure 4- 3 Topology of three-phase full-bridge inverter               | 42 |

| Figure 4- 4 Topology of three-phase full-bridge active rectifier       | 43 |

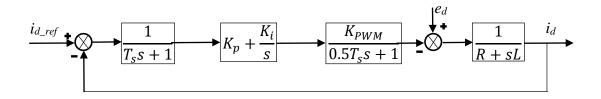

| Figure 4- 5 d-component of current-loop control diagram                | 46 |

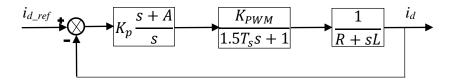

| Figure 4- 6 Simplified current-loop control                            | 47 |

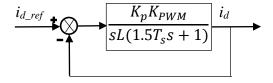

| Figure 4- 7 Final d-component of current-loop control                  | 47 |

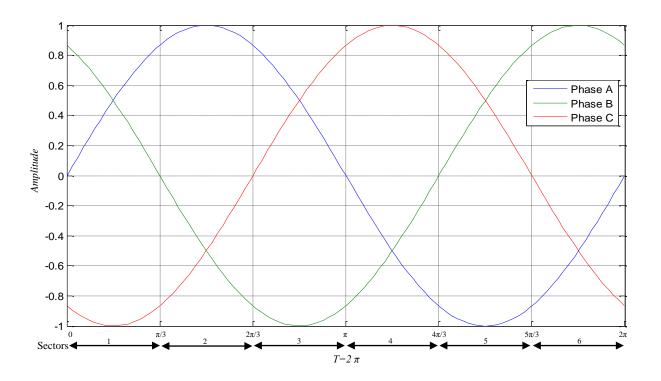

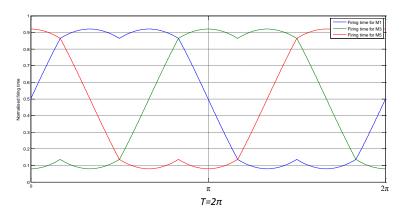

| Figure 4- 8 Normalised sinusoidal waves of three-phase voltage         | 54 |

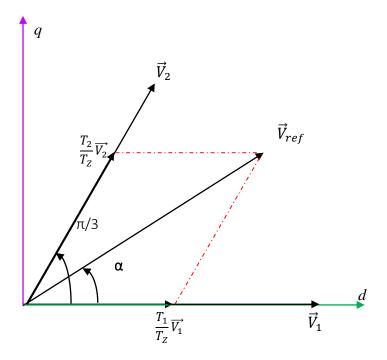

| Figure 4- 9 Vector synthesis schematic in sector 1                     | 56 |

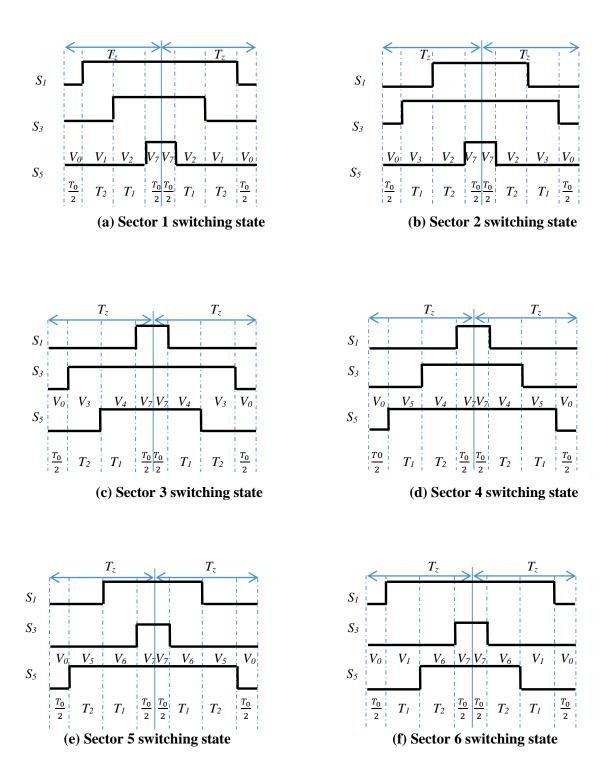

| Figure 4- 10 The patterns of voltage vectors                           | 58 |

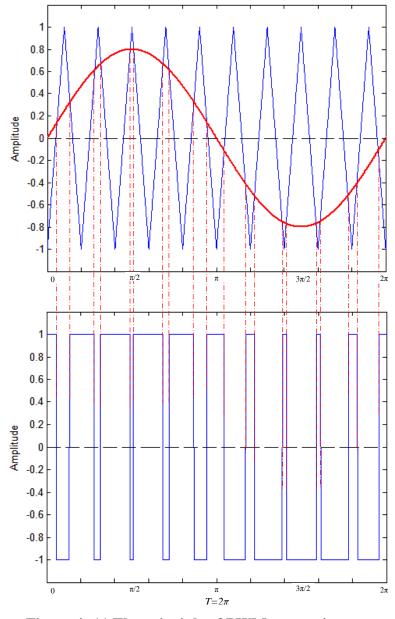

| Figure 4- 11 The principle of PWM generation                           | 61 |

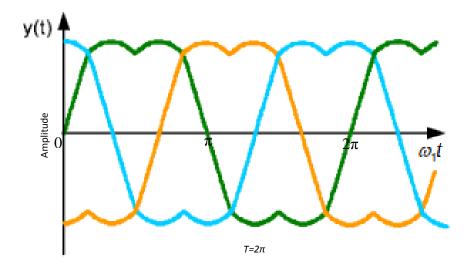

| Figure 4- 12 Ideal modulation waveform of SVPWM                        | 62 |

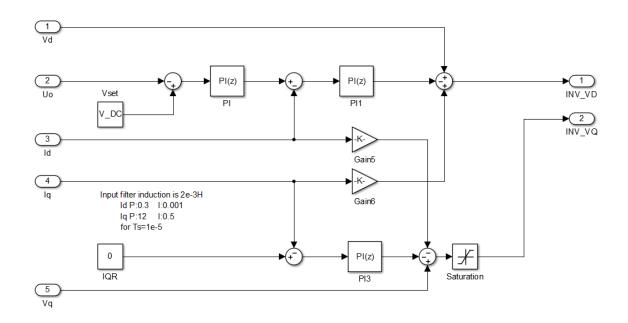

| Figure 4- 13 Modelling of current controlled-loop                      | 63 |

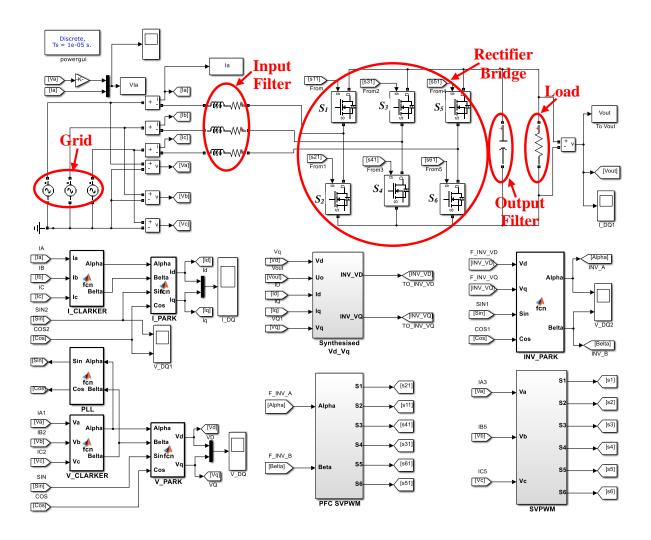

| Figure 4- 14 Modelling of three-phase SVPWM rectifier with/without PFC | 64 |

| Figure 4- 15 Generated saddled modulation waveform                     | 65 |

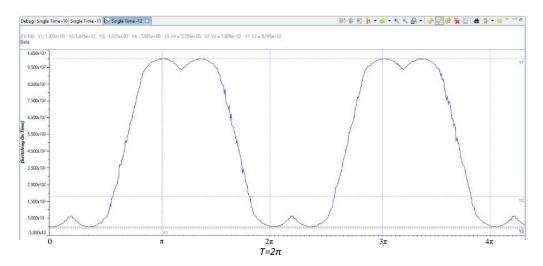

| Figure 4- 16 Experiment result of Phase A saddled carried waveform     | 66 |

| Figure 4- 17 Experiment result of Phase B saddled carried waveform     | 66 |

| Figure 4- 18 Experiment result of Phase C saddled carried waveform     | 66 |

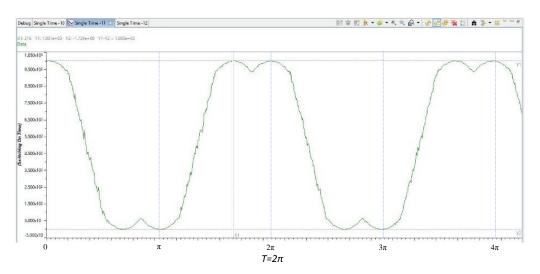

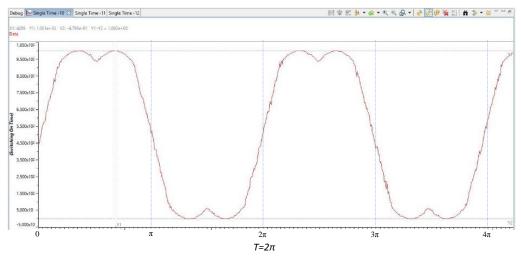

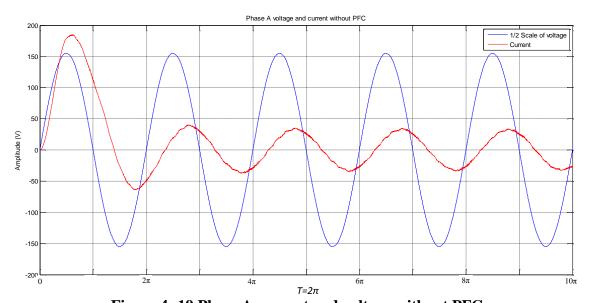

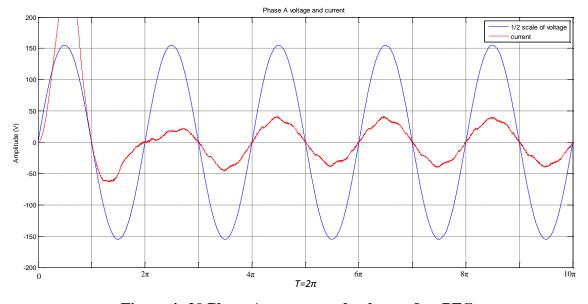

| Figure 4- 19 Phase A current and voltage without PFC                   | 67 |

| Figure 4- 20 Phase A current and voltage after PFC                     | 67 |

| Figure 4- 21 Analysis of harmonic distortion                           | 68 |

| Figure 4- 22 Experimental results                                      | 69 |

| Figure 4- 23 Strategy of singlephase rectifier with PFC                | 70 |

| Figure 4- 24 Model of single-phase rectifier with PFC                  | 71 |

| Figure 4- 25 Results of single-phase rectifier                         | 72 |

| Figure 4- 26 Harmonic analysis of input current                | 72  |

|----------------------------------------------------------------|-----|

| Figure 5- 1 Topology of buck converter                         | 75  |

| Figure 5- 2 Circuit of boost converter                         | 77  |

| Figure 5- 3 Basic interleaved boost topology                   | 79  |

| Figure 5- 4 Conventional boost circuit model                   | 81  |

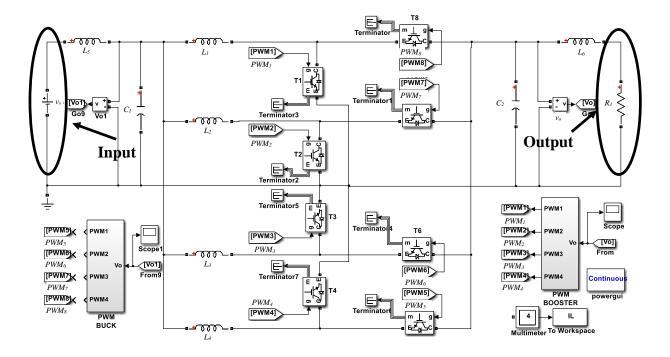

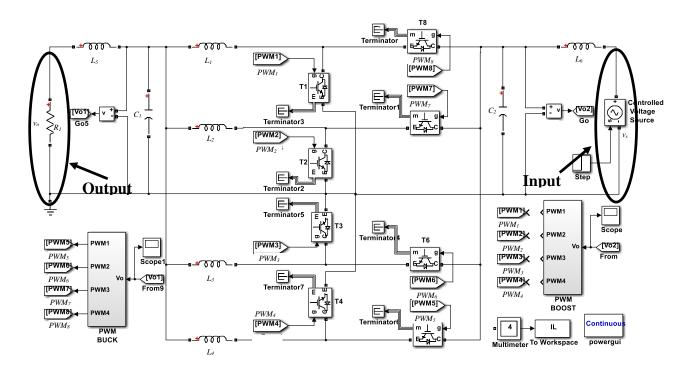

| Figure 5- 5 Simulation of four-phase IBDBBC circuit            | 81  |

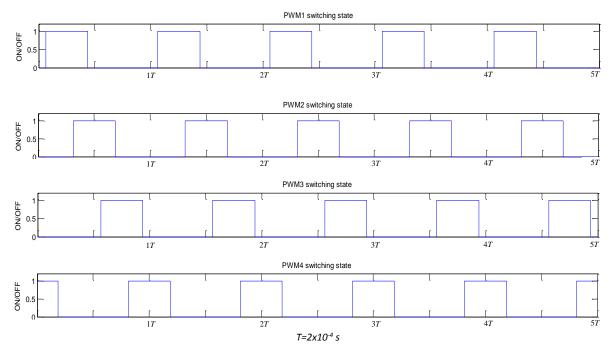

| Figure 5- 6 Generated PWM signals                              | 83  |

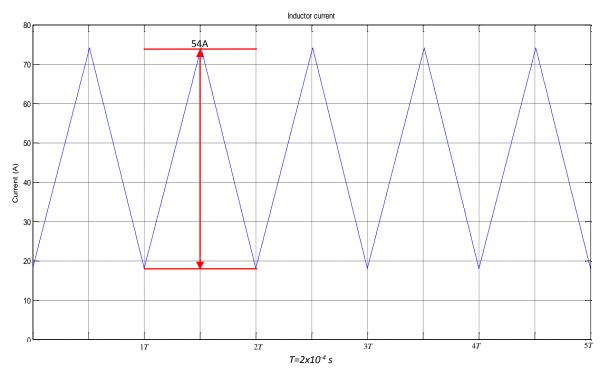

| Figure 5- 7 Inductor current of conventional CCM boost circuit | 83  |

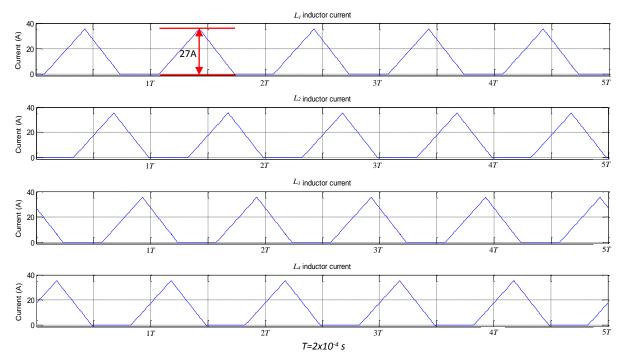

| Figure 5- 8 Inductor currents of IBDBBC circuit                | 84  |

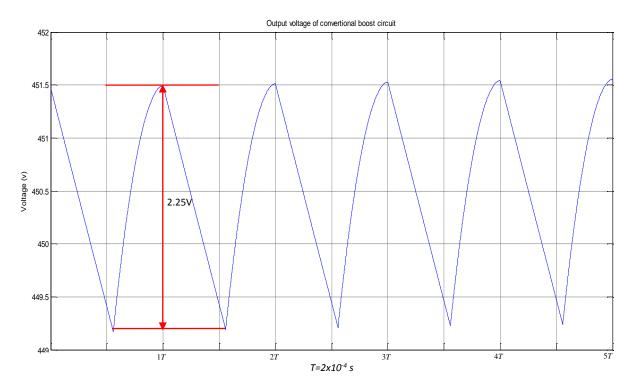

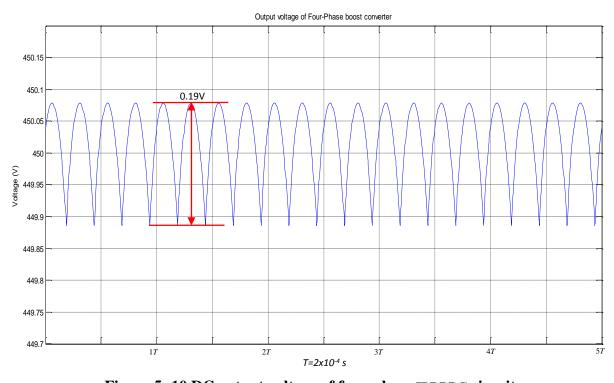

| Figure 5- 9 DC output voltage of conventional boost circuit    | 85  |

| Figure 5- 10 DC output voltage of four-phase IBDBBC circuit    | 85  |

| Figure 5- 11 Simulation of four-phase IBDBBC under buck mode   | 86  |

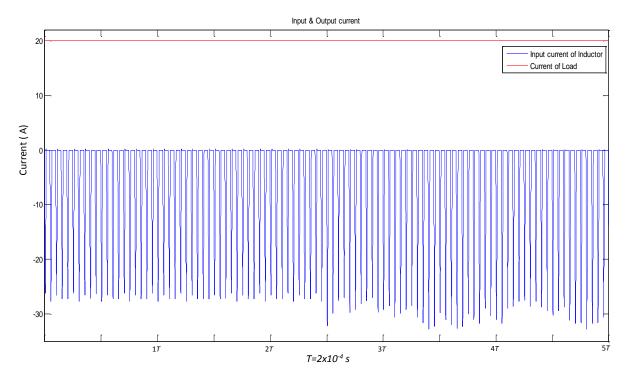

| Figure 5- 12 Input and output current                          | 87  |

| Figure 5- 13 Input and output voltage                          | 88  |

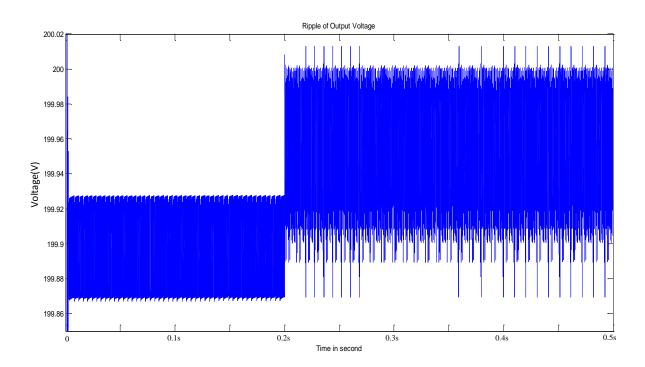

| Figure 5- 14 Output voltage ripple                             | 88  |

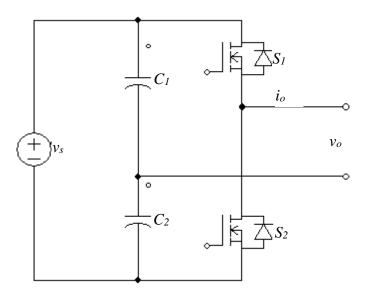

| Figure 6- 1 Topology of half-bridge single-phase VSI           | 93  |

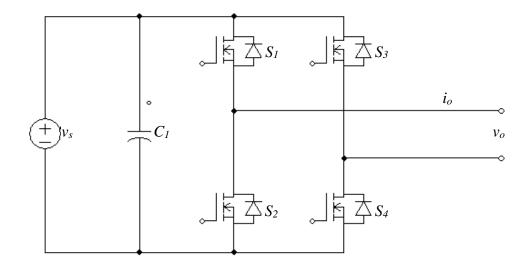

| Figure 6- 2 The topology of full-bridge single-phase VSI       | 94  |

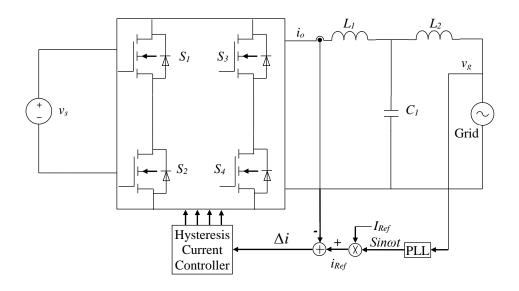

| Figure 6- 3 Structure of DC/AC inverter based on HCC           | 95  |

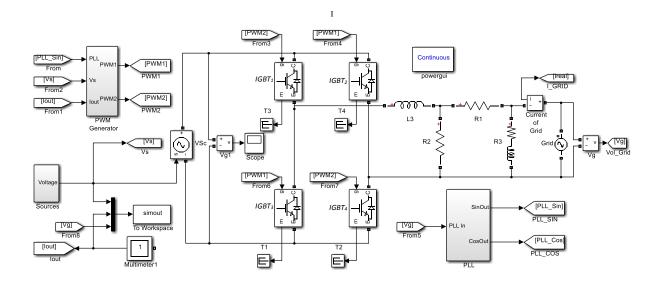

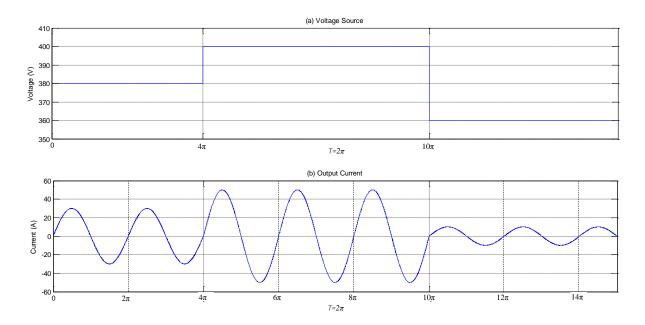

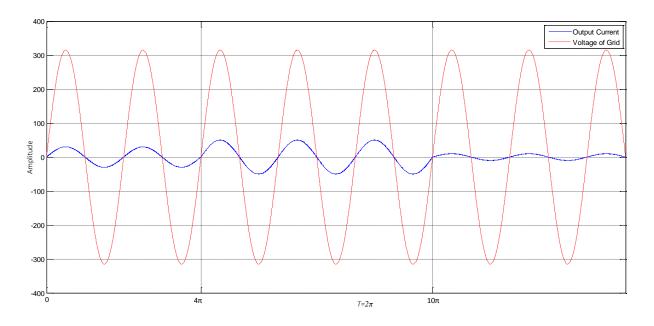

| Figure 6- 4 Simulation model of conventional PLL for GCI       | 96  |

| Figure 6- 5 Simulation model of full-bridge single-phase GCI   | 97  |

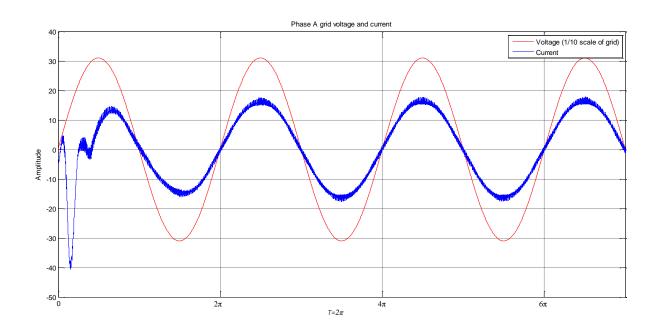

| Figure 6- 6 Simulation results of full-bridge single-phase GCI | 98  |

| Figure 6- 7 Output current of conventional GCI                 | 98  |

| Figure 6- 8 Schematic diagram of GCI                           | 99  |

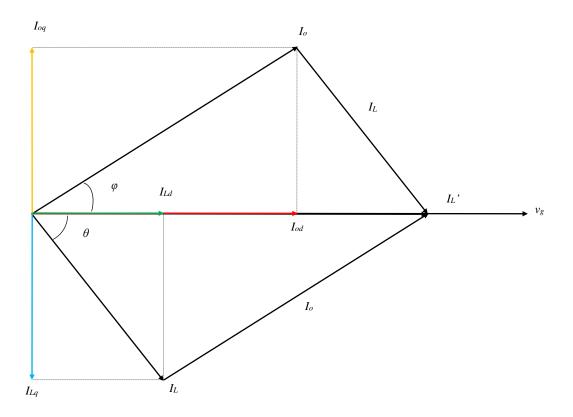

| Figure 6- 9 Vector relationships of GCI                        | 100 |

| Figure 6- 10 PCC of single-phases system                       | 101 |

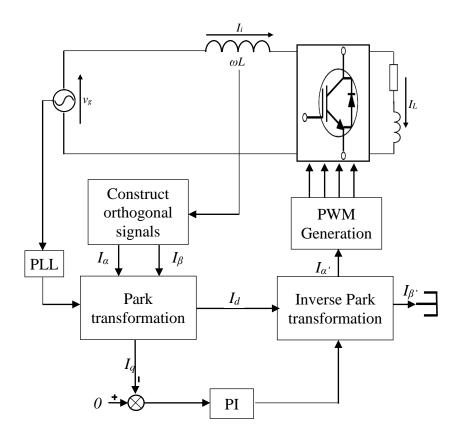

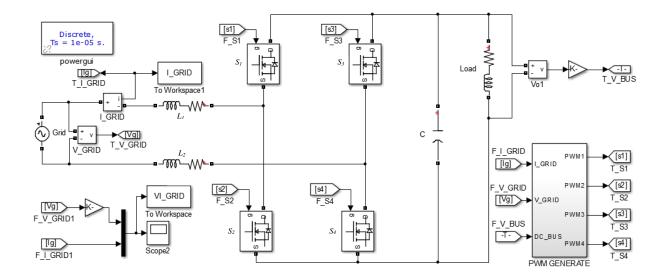

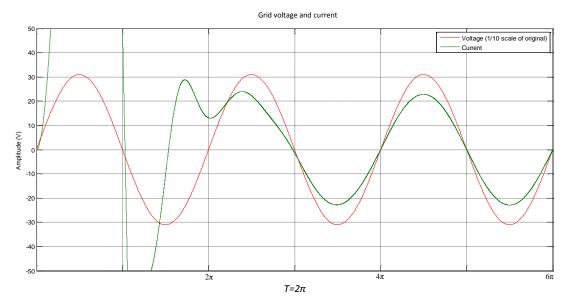

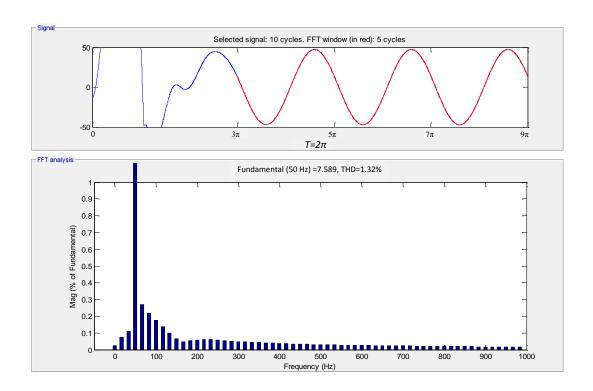

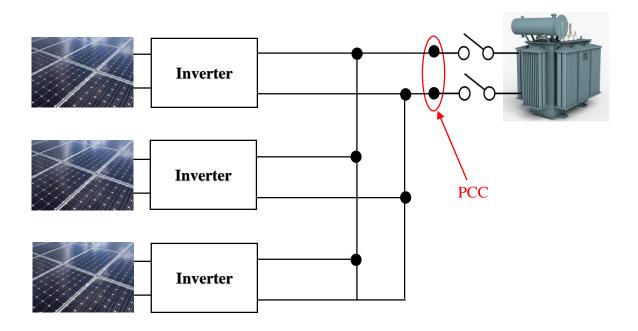

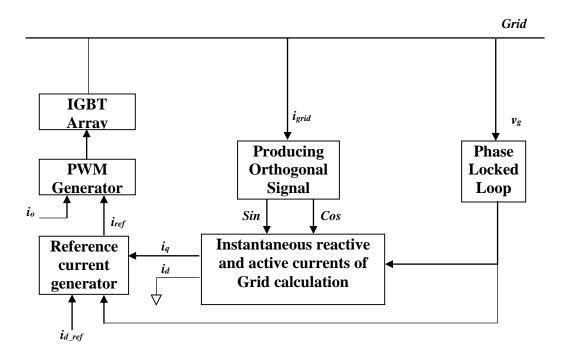

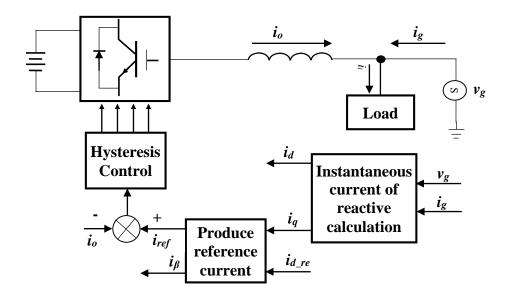

| Figure 6- 11 Structure of control algorithm                  | 102 |

|--------------------------------------------------------------|-----|

| Figure 6- 12 Diagram of RPC                                  | 104 |

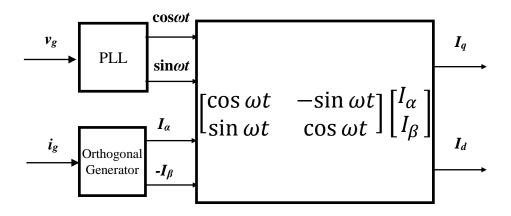

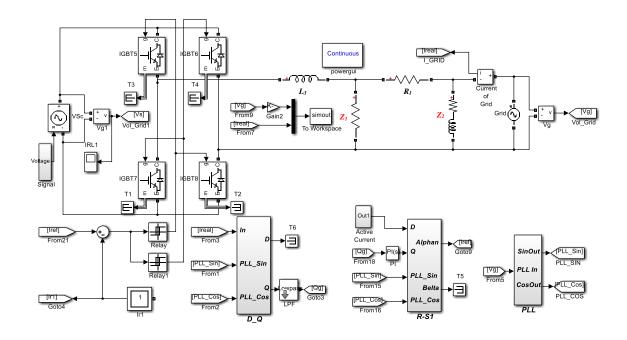

| Figure 6- 13 Split instantaneous active and reactive current | 104 |

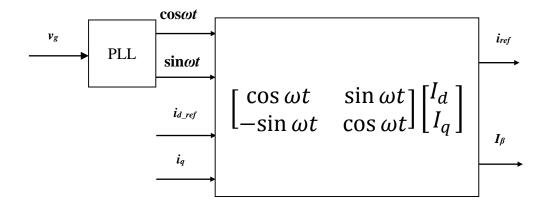

| Figure 6- 14 Generated reference current                     | 105 |

### **Contents**

| AcknowledgementsII                                                                  |

|-------------------------------------------------------------------------------------|

| AbstractIII                                                                         |

| AbbreviationsV                                                                      |

| List of FiguresVIII                                                                 |

| Chapter 1 Introduction                                                              |

| 1.1 Motivation                                                                      |

| 1.2 Aims and objectives                                                             |

| 1.3 State of the art technologies6                                                  |

| 1.3.1 Techniques related to RPC                                                     |

| 1.3.2 Techniques for energy storage9                                                |

| 1.4 Major contributions9                                                            |

| 1.4.1 GCI output with RPC9                                                          |

| 1.4.2 Interleaved bi-directional DC/DC converter for charging/discharging battery10 |

| 1.4.3 MRes dissertation and publications                                            |

| 1.5 Outline of the thesis                                                           |

| Chapter 2 Experimental Environment                                                  |

| 2.1 Introduction12                                                                  |

| 2.2 Hardware environment                                                            |

| 2.2.1 C2000 Solar PV inverter development board                                     |

| 2.2.2 NXP LPC 2132 ARM16                                                            |

| 2.2.3 TMS320F28335 DSP                         | 16 |

|------------------------------------------------|----|

| 2.2.4 Insulated-gate bipolar transistor (IGBT) | 17 |

| 2.2.5 Voltage and current transducers          | 18 |

| 2.3 Software environment                       | 20 |

| 2.3.1 MATLAB/Simulink                          | 20 |

| 2.3.2 Keil uVision                             | 20 |

| 2.3.3 Code composer studio                     | 21 |

| 2.4 Mathematical tools                         | 21 |

| 2.4.1 Clarke's transformation                  | 21 |

| 2.4.2 Inverter Clarke's transformation         | 23 |

| 2.4.3 Park's transformation                    | 23 |

| 2.4.4 Inverse Park's transformation            | 24 |

| 2.4.5 P-Q theory                               | 25 |

| 2.5 Summary                                    | 26 |

| Chapter 3 Phase-Locked Loop                    | 27 |

| 3.1 Introduction                               | 27 |

| 3.2 Generic PLL                                | 28 |

| 3.3 SOGISPLL mathematical model                | 29 |

| 3.4 Discrete Implementation of SOGIPLL         | 34 |

| 3.5 Simulation                                 | 35 |

| 3.6 Summary                                    | 37 |

| Chapter 4 AC to DC Rectifier                                    | 38 |

|-----------------------------------------------------------------|----|

| 4.1 Introduction                                                | 38 |

| 4.2 Mathematical model of three-phase active rectifier          | 43 |

| 4.3 Current loop design                                         | 46 |

| 4.4 Voltage loop design                                         | 49 |

| 4.5 Simulation of a three-phase SVPWM active rectifier          | 53 |

| 4.5.1 Identify sector                                           | 54 |

| 4.5.2 Determine firing time for switching devices               | 56 |

| 4.5.3 Over modulation                                           | 60 |

| 4.5.4 Generating controlled PWM for SVPWM                       | 61 |

| 4.6 Modelling three-phase SVPWM rectifier                       | 62 |

| 4.6.1 Modelling identify area and firing time                   | 63 |

| 4.7 Modelling single-phase rectifier                            | 70 |

| 4.8 Summary                                                     | 72 |

| Chapter 5 Bi-directional interleaved boost/buck DC/DC converter | 74 |

| 5.1 Introduction                                                | 74 |

| 5.2 Buck converter                                              | 75 |

| 5.3 Boost converter                                             | 77 |

| 5.4 Interleaved boost circuit                                   | 79 |

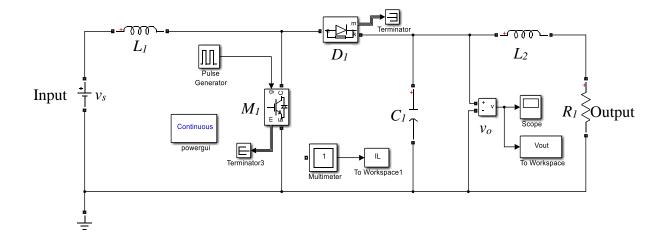

| 5.5 Modelling four-phase IBDBBC under boost mode                | 80 |

| 5.6 Modelling four-phase IBDBBC under buck mode                 | 86 |

| 5.7 Summary                                                     | 89  |

|-----------------------------------------------------------------|-----|

| Chapter 6 GCI with RPC                                          | 90  |

| 6.1 Introduction                                                | 90  |

| 6.2 Topologies of a GCI                                         | 92  |

| 6.3 GCI based on HCC                                            | 94  |

| 6.4 Simulation of conventional single-phase GCI                 | 95  |

| 6.5 RPC                                                         | 99  |

| 6.5.1 Control strategies                                        | 101 |

| 6.6 Simulation of single-phase GCI with RPC                     | 105 |

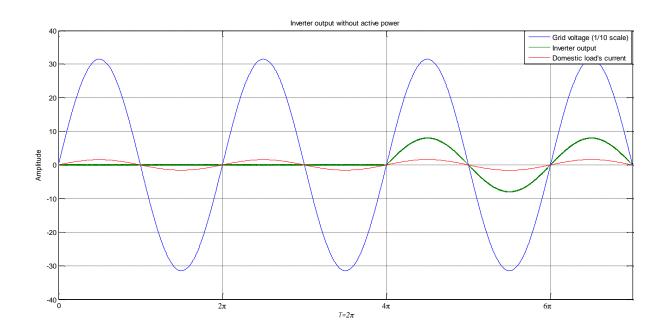

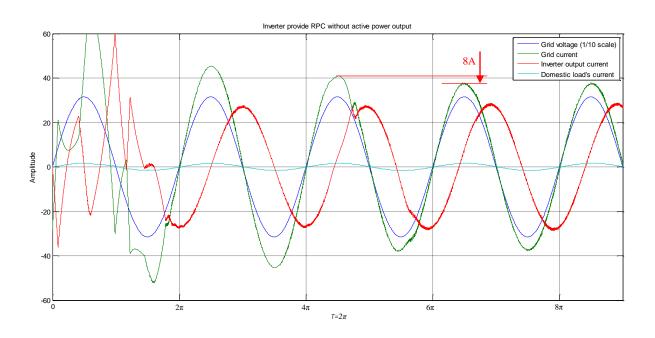

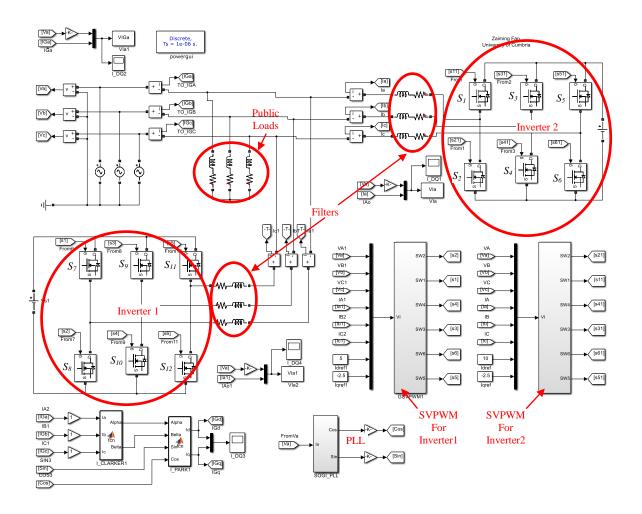

| 6.7 Simulation of three-phase GCI with RPC                      | 112 |

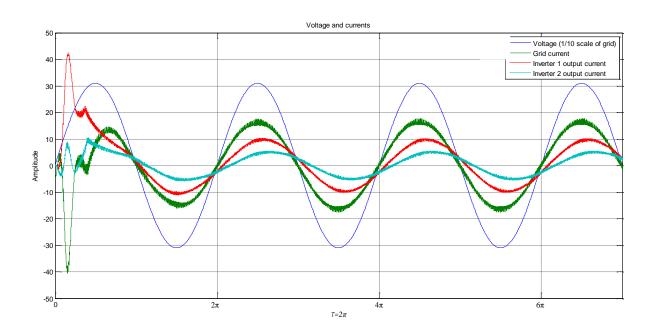

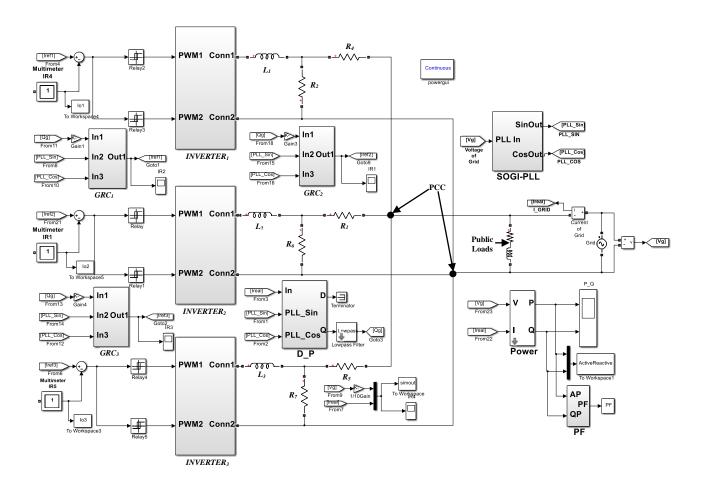

| 6.8 Modelling of multi-inverter with RPC                        | 114 |

| 6.9 Experimental verification of off-grid inverters             | 118 |

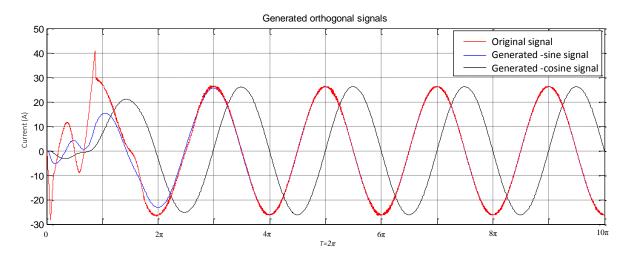

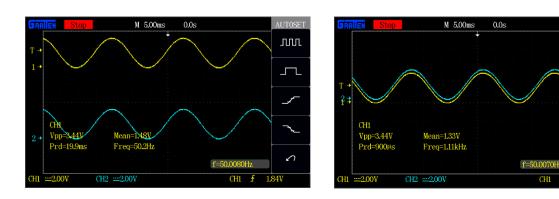

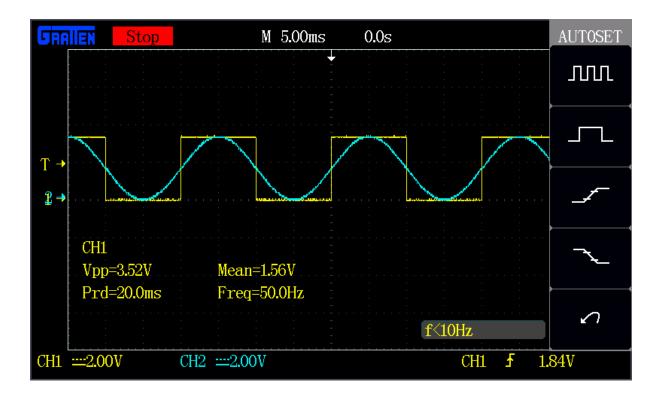

| 6.9.1 Generating synchronous signal                             | 119 |

| 6.9.2 Frequency synchronisation                                 | 121 |

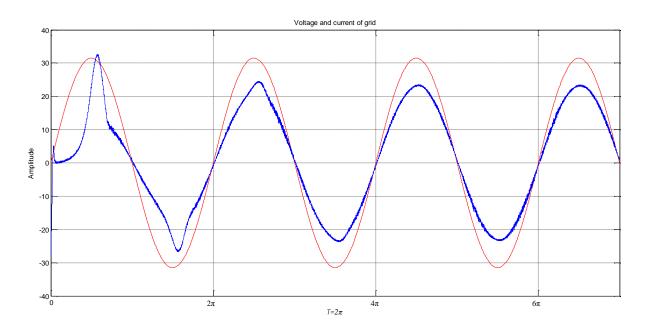

| 6.9.3 Experiment and results                                    | 121 |

| 6.10 Summary                                                    | 123 |

| Chapter 7 Conclusions and Future Work                           | 124 |

| 7.1 Conclusions and Discussion                                  | 124 |

| 7.2 Future work                                                 | 126 |

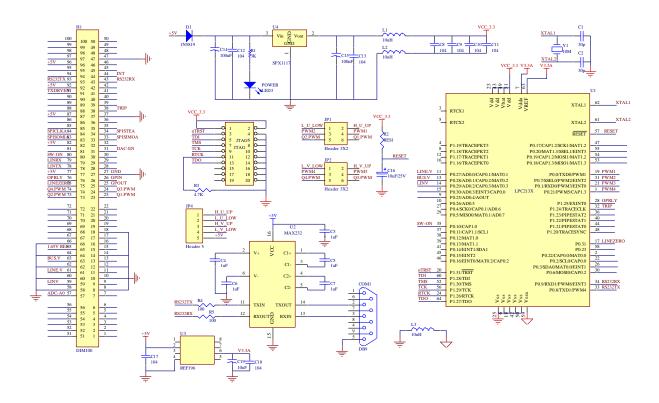

| Appendix A Schematic Of Control Board For Single-Phase Inverter | 127 |

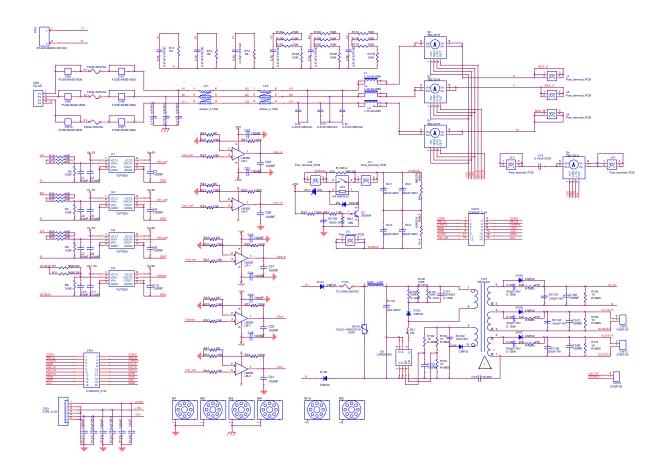

| Appendix B Schematic Of Sensors                                 | 128 |

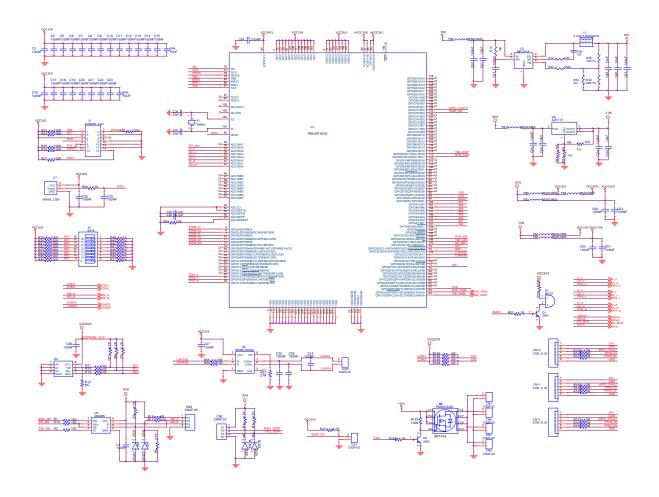

| Appendix C Schematic Of Main Control For Rectifier | 129 |

|----------------------------------------------------|-----|

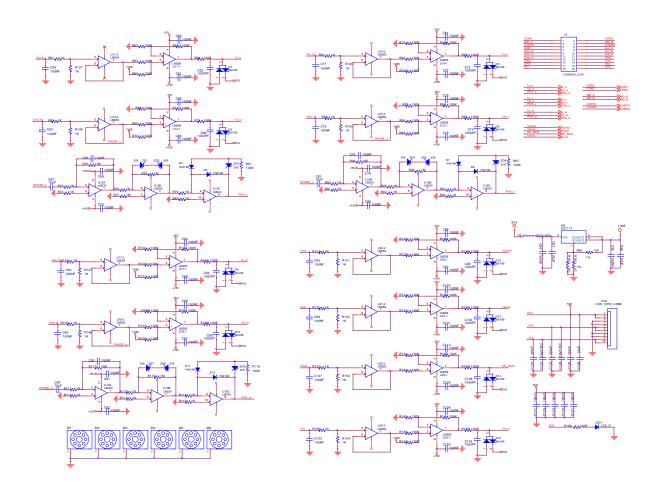

| Appendix D Schematic Of Signal Pre-Processing      | 130 |

| Appendix E MATLAB Function Program                 | 131 |

| E.1 Clarke's transformation                        | 131 |

| E.2 Park's transformation                          | 131 |

| E.3 Inverse Park's transformation                  | 131 |

| E.4 Identify area                                  | 131 |

| E.5 Firing time calculation                        | 132 |

| Appendix F Central Control Program                 | 134 |

| F.1 Main function codes                            | 134 |

| F.2 Configure PLL                                  | 134 |

| F.3 Timer 0 codes                                  | 135 |

| Appendix G Inverter Program                        | 137 |

| G.1 Main function codes                            | 137 |

| G.2 Extern interrupts codes                        | 141 |

| G.3 Timer 0 codes                                  | 144 |

| G.4 PWM generator codes                            | 148 |

| Appendix H Three-phase SVPWM Rectifier Program     | 151 |

| H.1 Three-phase rectifier with PFC codes           | 151 |

| H.2 SVPWM generation                               | 166 |

| H.3 ADC sampling codes                             | 170 |

| References | 7 | / |

|------------|---|---|

|            |   |   |

### **Chapter 1 Introduction**

### 1.1 Motivation

In the past two decades, renewable power generation, such as wind and solar power, have experienced a considerable growth due to the problems the world faces in the dual challenges of fossil fuel depletion and carbon dioxide emissions (Fthenakis, et al., 2009). However the intermittent nature of renewable energy sources (typically wind and solar energy sources) is a major issue for the renewable power industry. DC/AC inverters play a key role in renewable power generation, which interfaces renewable power generators with the grid. However, a conventional GCI injects power from the renewable power generator directly into the grid, which fluctuates with the intermittent and unstable renewable energy sources.

Furthermore, the increase in generation uncertainty created by intermittent sources, such as photovoltaic (PV) cells and wind turbines, presents a challenge to the system stability of large power grids (Eltawil & Zhao, 2010). Renewable energy sources such as solar and wind are intermittent energy resources, especially as wind speeds and cloud movements cannot be accurately forecast in real time. For the solar energy, the maximum solar radiation occurs at around 13:00 hours each day. That means the power output of a solar PV panel theoretically reaches its maximum at this time despite the domestic demand being minimum. Therefore renewable power systems may operate in troughs of power demand, however the GCIs with an MPPT still output power into the grid in accordance with the code of compliance. Therefore, this may cause a voltage rise in the utility grid, which could result in the generation system being forced to be disconnected from the power grid when the voltage of the utility grid reaches its top limit.

Moreover, for a utility grid to operate properly, it is a prerequisite for GCIs to inject power into the grid when power is available. This means the primary issue of a GCI not being able to generate power even under the situation of best weather conditions for generation while the power grid is cut off for a reason either foreseeable (such as scheduled maintenance and power curtailment when power supply does not meet demand in general) or unforeseeable incidence (such as fire, flood). This is especially the case in some areas of the power system which are relatively vulnerable such as in developing countries in Saharan Africa and South-Asian where there are excellent solar energy sources, but unreliable or unavailable electricity grids.

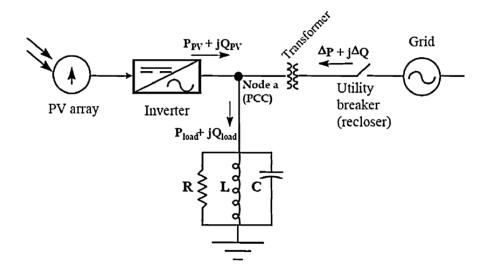

Figure 1-1 Conventional RPC for solar PV power system

Taken from (Eltawil & Zhao, 2010)

In addition, the increasing application of nonlinear loads, such as induction cookers, large variable frequency drives (VFD), switching-power supplies, induction motors and welding machine, may cause distribution system power quality issues, especially the production of a significant amount of reactive power and harmonics (Renukadevi & Jayanand, 2015). However, conventional distributed generation systems have limited capability to RPC. The use of a complementary external passive parallel RLC (resistor, inductor and capacitor) components or static synchronous compensator (STACOM) at the point common coupling

(PCC) shown in Figure 1-1 can provide compensation (Medina, et al., 2016). This increases the system and operation cost.

Finally, Llaria and Chicco presented that a system based on small-scale cogeneration could be more suitable than a large-scale distributed generation (Llaria, et al., 2011) (Chicco & Mancarella, 2009). Residential roof mounted solar PV system can be considered as a small-scale generation, so each individual small-scale system like that, connected to the same substation or community, can constitute a micro-grid system. But for the residential roof mounted solar PV system or commercial small-scale renewable power system, using Economy 7, a type of electricity tariff based on the time of use, the price of electricity on Economy 7 is very low during night, however night-time is the period of the lowest electricity consumption.

### 1.2 Aims and objectives

This thesis aims

- 1) To develop a bi-directional GCI with RPC for a micro-grid by using interconnected small-scale GCIs sharing responsibility for community reactive power.

- 2) To develop an interleaved bi-directional boost/buck direction current to direction current (DC/DC) converter interfacing the DC link and the battery bank for charging/discharging batteries.

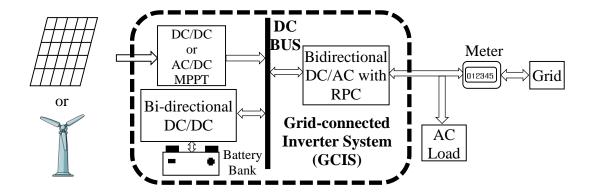

To mitigate the output voltage fluctuation from GCIs and improve customers' profitability, a battery bank at the inverter DC side, is included, interfaced by a bi-directional DC/DC converter with a DC-Bus as shown in Figure 1-2. In the community micro-grid, each individual inverter only injects excess power into the utility grid, generated from the renewable energy source (RES), with the premise that the battery bank is fully charged and the customers' requirements are completely met. During low tariff periods the inverter can be operated as an AC/DC controllable active rectifier to draw power from the utility grid to provide energy to

charge the battery bank by means of the bi-directional boost/buck DC/DC converter. Therefore, the inverter with those two control rules can minimise the end-user's electricity costs.

Figure 1-2 Proposed the diagram of small-scale GCIS

Figure 1-2 presents the community micro-grid formed with a number of individual small-scale GCI system (GCIS), in which, the GCIS is integrated with a maximum power point tracking (MPPT) regulated DC/DC converter connecting solar PV panels or AC/DC converter connecting wind turbine generator, a bi-directional boos-buck DC/DC converters for charging/discharging batteries, and a bi-directional DC/AC inverter with RPC interfacing the DC bus and AC grid. A single GCI cannot provide RPC for a whole system, if each GCIS in the micro-grid system can quantitatively share responsibility RPC for whole system, then the conventional RPC devices or equipment illustrated in Figure 1-1 can be removed at the PCC node.

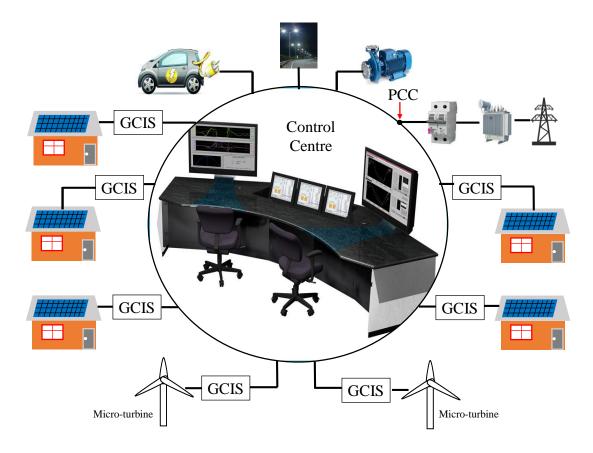

Figure 1-3 illustrates a diagram of micro-grid system, which consists of solar PV generations, wind turbines, electrical vehicle (EV), public utilities, GCISs and control centre. The Presented GCIS is used to interface between distributed sources and micro-grid.

Figure 1-3 Diagram of smart distributed micro-grid

There are a number of established algorithms that can be employed to implement MPPT for both wind turbines and solar PV systems. Therefore, the MPPT algorithms are not considered in this thesis. To develop a smart GCIS for the micro-grid, the objectives of the project are:

- To investigate the design process of a phase-locked loop (PLL) based on second order generalised integrator (SOGIPLL) for synchronising with the grid voltage and constructing orthogonal signals.

- 2. To model a bi-directional multi-phase interleaved boost/buck DC/DC converter.

- To model an active rectifier with PFC based on the topologies of GCI for single-phase system.

- 4. To model a controllable active space vector pulse width modulation (SVPWM) rectifier with PFC based on the topologies of GCI for three-phase system.

- 5. To model a dispatchable single-phase hysteresis band GCI with RPC.

- 6. To model a dispatchable three-phase SVPWM GCI with RPC.

- 7. To model multi-inverter sharing RPC for a micro-grid.

- 8. To compare the results of modelling with measurements on a laboratory system.

### 1.3 State of the art technologies

Nowadays, with technological developments, many clean renewable energy resources, such as solar, wind, hydro, tidal and biomass power are being utilised without emissions. Although renewable energy resources are clean and favoured by researchers for generation, the high penetration of renewable energy in distributed generation is associated with many new technical challenges in practical applications, such as grid voltage fluctuation, frequency regulation and RPC. Thereby, large amount of GCIs without proper technical infrastructure could have an impact and place significant harmonic stress on the electricity grid (Obi & Bass, 2016), unless the increasing GCIs have the dispatchable characteristics (Zarina, et al., 2012). Hence, during recent years, the micro-grid concept has been introduced, consisting of several alternative sources which can be considered plug-in or –out, while distributing electricity more efficiently and securely (Aghajani, et al., 2015) (Kamankesh, et al., 2016).

A micro-grid is commonly defined as a small community of interconnected loads and small-scale distributed generators (DGs) which can be dispatched or regulated by a control centre. A micro-grid is typically supplied by a MV/LV substation, and generally comprises DG, a smart meter and information communication (Sbordone, et al., 2016). The DG interfaces the resource and the micro-grid, it plays an important role, with the features of maintaining voltage balance, provide peak-shaving, optimise energy flux, and offer auxiliary services, which can be easily plugged-in or -out.

In the future, the numerous unpredictable loads introduced into the micro-grid, such as the expected increase of a number of EV charging stations, could bring chaos to a distributed grid

that has been fluctuating due to the intermittent nature of renewable energy sources. Sbordone et al propose solving these problems (Sbordone, et al., 2016) by the concept of integrating autonomous energy storage system at a location near the substation for reducing variability of power flow, providing balancing support, peak-shaving and load shifting. Panwar et al. present a strategy of incorporating regenerative fuel cells and EVs to solve the problem discussed above (Panwar, et al., 2015). Though the approach of configuring storage devices near a substation could enhance the stability of an entire distributed grid system, for a distributed micro-grid system, except the stabilising the grid, and minimising the user's costs which is also an important factor to be considered.

The voltage source inverter (VSI) is the most widely employed topology for this role with some common filter circuits, L (inductor) or LCL (inductor, capacitor and inductor), to achieve a DC/AC GCI for distributed generation (Sampaio, et al., 2016). Several related papers present various current control algorithms to feed active power into the grid. In order to enhance the stability of the grid system, the requirement of RPC has drawn more interest from researchers in the past few years.

#### 1.3.1 Techniques related to RPC

The most common volt amperes reactive (VAR) control approach for both small-scale and large-scale distributed generation is ensuring the inverter operates at a constant, unity power factor. The approach of utilising large passive capacitive banks or STACOM, at the PCC node, to maintain unity power factor is widely used. However, the major drawback of these approaches is not being able to inject RPC back to the grid. In other words, these approaches do not offer RPC for domestic loads. Variable power factor is a popular method, in which an inverse relationship between  $\frac{\Delta P}{\Delta Q}$  and the ratio of  $\frac{R}{X}$  at the PCC is established by setting the voltage variation difference to 0 (Smith, et al., 2011). This method observes the voltage

changes at the PCC to determine the extent of RPC. This is rather similar to the droop control technique, in which active power changing affects the grid frequency and reactive power influences grid voltage magnitude (Samadi, et al., 2014) (Rouzbehi, et al., 2014).

Sampaio et al. present, according to active and reactive power transfer, a strategy to control the power transfer angle by means of stabilising active power output and to control reactive power by reducing voltage magnitude fluctuation, which is actually quite similar to the droop control (Sampaio, et al., 2016).

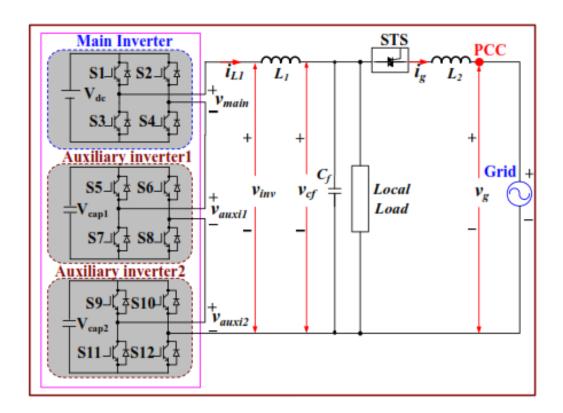

Liu et al. proposed a topology of a single-stage for a single-phase GCI with wide range RPC, in which 3 full-bridge inverters are connected in series. One of the inverters injects active power into the main grid, and the other two auxiliary inverters interface dedicated energy storage for the grid, providing RPC, see Figure 1-4 (Liu, et al., 2010).

Figure 1-4 Topology of single-stage GCI

Taken from (Liu, et al., 2010)

#### 1.3.2 Techniques for energy storage

Energy storage systems (ESS) can be traced back to early last century when power generation was often shut down overnight because power electronics control technology was not available (Baker & Collinson, 1999) (Suberu, et al., 2014) (Chen, et al., 2009). Initially, the commonly used ESS approach for peak-shaving in practical applications was hydroelectric pumped storage (HPS). With the technical development of storage, there are variety of storage media, including HPS, compressed air, flywheel, battery, flow battery, capacitor or supercapacitor, superconducting magnet, solar fuels and thermal energy storage (Luo, et al., 2015) (Kousksou, et al., 2014) (Rodrigues, et al., 2014) (Abdin, et al., 2015).

In recent years, integrating ESS into distributed generation systems has attracted many researchers' attention, associated with high penetration of renewable energy generation with unpredictable power fluctuation. These ESS especially include battery systems technology, which is the most widespread energy storage device for power applications. Batteries can be configured in different sizes with wide capacities ranging from watt-hours to gigawatt-hours (Aneke & Wang, 2016). There are many articles proposing a variety of applications aimed at mitigating fluctuation, balancing intermittency of wind or other renewables and RPC, by means of installing a central ESS close to the electrical substation (Suberu, et al., 2014) (Chicco & Mancarella, 2009) (Chen, et al., 2009).

### 1.4 Major contributions

#### 1.4.1 GCI output with RPC

The thesis describes a novel algorithm, based on D-Q theory, to split the active and reactive currents, to quantitatively control active and reactive power for GCI.

#### 1.4.2 Interleaved bi-directional DC/DC converter for charging/discharging battery

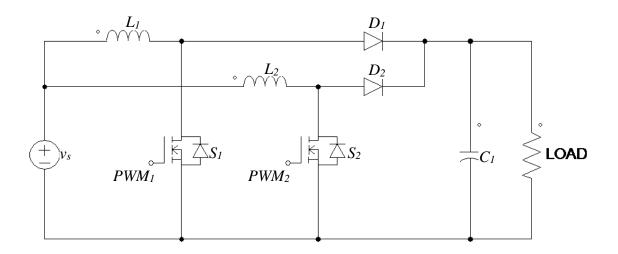

In order to reduce the ripple of converter current and improve thermal dissipation issue, the thesis presents a topology of four-phase interleaved bi-directional DC/DC boost/buck converter (IDBBBC) for charging/discharging battery.

#### 1.4.3 MRes dissertation and publications

- 1. Fan, Z. & Liu, X., 2015. Smart Inverter with Active Power Control and Reactive Power Compensation. Journal of Electrical and Electronic Engineering, pp. 139-145.

- 2. Fan, Z., 2012. Mathematical Modelling of Grid Connected Fixed-Pitch Variable-Speed Permanent Magnet Synchronous Generators for Wind Turbines, Preston: UCLAN.

- 3. Fan, Z. & Liu, X., 2012. A novel universal voltage sag detection algorithm. Power Engineering and Automation Conference (PEAM), *IEEE publisher*.

- 4. Wen, C., Lu, G., Wang, P., Li, Z., Liu, X., Fan, Z., 2011. Vector control strategy for small-scale grid-connected PMSG wind turbine converter *Innovative Smart Grid Technologies (ISGT Europe) conference, IEEE publisher*.

- 5. Fan, Z. & Liu, X., Reactive power compensation for single-phase inverter in microgrid submitted to International Journal of Advanced Engineering Research and Science to be reviewed.

### 1.5 Outline of the thesis

The structure of the thesis is as follows: In order to demonstrate methodologies and algorithms, simulations and experiments have been carried out which require specific software tools and hardware development kits to support them.

Chapter 2 describes the software tools, integrated development environment (IDE), the hardware development kit and mathematical tools.

Chapter 3 describes the step-by-step procedures on how to design a SOGIPLL for an embedded real time system and an algorithm, which is demonstrated through MATLAB/Simulink modelling and hardware implementation. PLL as a fundamental function for GCI plays a key role for an on-grid system.

Chapter 4 describes in detail the design of a three-phase SVPWM rectifier through constructing a pair of orthogonal signals for single-phase current, adopting Clarke's and Park's transformation into a single-phase system to split active and reactive current for a single-phase system. The modelling of both three-phase and single-phase rectifiers, and experimental work based on a three-phase SVPWM rectifier are conducted.

Chapter 5 describes the modelling of a four-phase, bi-directional, interleaved, boost/buck DC/DC converter, which can be an ideal charging/discharging converter for the battery storage in a micro-grid.

Chapter 6 presents a smart dispatchable GCI with RPC and the simulation model of multiinverters synergistically providing RPC for a micro-grid.

Chapter 7 concludes the project with discussion of the project outcomes and briefs future research directions.

### **Chapter 2 Experimental Environment**

### 2.1 Introduction

In order to achieve power flow bi-directionally in a micro-grid, some key factors must to be taken into account for building an experimental environment for a three-phase system achieve rectifier, based on a GCI topology. Another experimental environment for a single-phase GCI built to demonstrate multi-inverters operating synchronously in a stand-alone system without grid support.

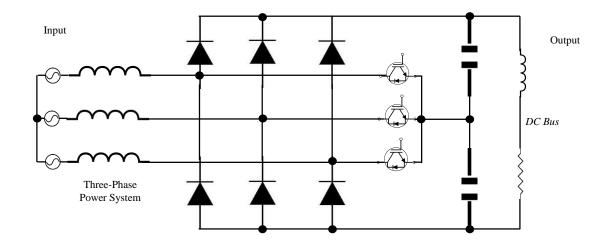

Because the purpose of the rectifier is to achieve bi-directional power flow based on the inverter topology, Figure 2-1 illustrates a bi-directional rectifier/inverter topology in three-phase system consisting of 6 switching devices, if swapping the input and output in the figure, the system can be considered as the conventional three-phase inverter. This requires 6 PWM signal channels, and 3 sampling of phase voltages, and currents and 1 of DC bus voltage, totally requiring 7 channels of analogue to digital (AD) signal conversion. Another issue which has to be considered is to minimise filter inductance size before output by increasing the PWM signal frequency. Moreover, the algorithms for a three-phase SVPWM rectifier system contain complex trigonometrical functions and proportional-integral-derivative (PID) control which require mathematical floating point calculations. Therefore, a high speed TMS320F28335 processor with built-in floating-point unit was utilised to implement the three-phase AC/DC rectifier system.

Figure 2-1 Structure of bi-directional three-phase rectifier/inverter topology

Digital Signal Processor (DSP) TMS320F28335 is a high-performance real-time controller with single-precision Floating-Point Unit (FPU) from Texas Instruments (TI). TMS320F28335 has a good number of peripheral ports, such as 18 PWM outputs and 16 channels 12-Bit ADC.

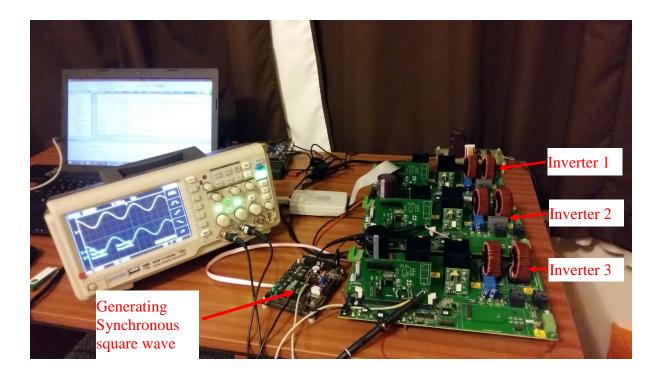

The C2000 Solar Inverter Development Kit (SDK) shown in Figure 2-2 is designed to achieve the general functions of a GCI. There are some special functions required by the thesis which need extra hardware to support them, such as inverter outputs synchronised with each other when operating in off-grid mode. Therefore, the control board has been re-designed by the author, as shown in Figure 2-4, to replace the original control board SDK shown in Figure 2-

3, using A LPC2132 NXP ARM microcontroller control the main board of the  $C2000^{\text{TM}}$  SDK and this is utilised to implementing a single-phase inverter controlled by a central controller, implemented on a LPC2132 development board, illustrated in Figure 2-5.

Figure 2- 2 The main board of  $C2000^{\text{TM}}$  SDK

Figure 2- 3 Control board of  $C2000^{\text{TM}}\text{SDK}$

Figure 2- 4 Re-designed control board

Figure 2-5 Central control board

C/C ++ was employed to program the controllers using CCS3.3 IDE and Keil uVision 4.0 for the TI DSP processor and ARM microcontroller respectively. All simulations in this thesis were modelled in MATLAB/SIMULINK; part of the algorithms have been conducted through experiments, such as SVPWM rectifier in three-phase system. Three GCI operate in standalone mode.

### 2.2 Hardware environment

### 2.2.1 C2000 Solar PV inverter development board

Figures 2-2 and 2-3 show the *C2000*<sup>TM</sup> SDK is a development platform based on a DSP C2000 Microcontroller from Texas Instruments. The Development Kit is a general and conventional inverter, which is insufficient to provide communications between the inverter and a central controller. Therefore, the circuit of the control part of the Inverter Development Kit was redesigned and the C2000 Microcontroller replaced by a NXP LPC2132 ARM microcontroller to implement the function of a standalone inverter, which was used to demonstrate the feasibility of solving synchronising issues under circumstances of multi-inverter operate in offgrid mode. In the experiment, only three inverters connected together operate in off-grid mode.

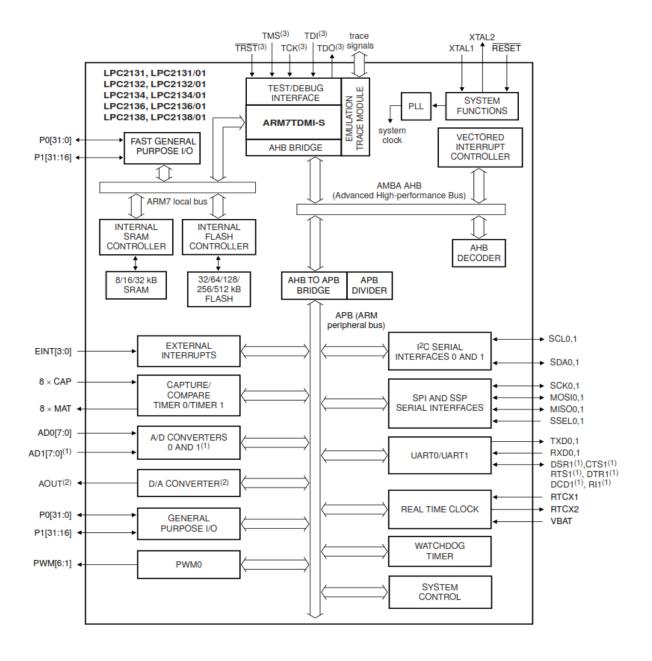

#### 2.2.2 NXP LPC 2132 ARM

The LPC2132 microcontroller is based on a 16/32-bit ARM7TDMI-S control processor unit (CPU) with real-time emulation and embedded trace support and a 64kB embedded high-speed flash memory. A 128-bit wide memory interface and unique accelerator architecture enable 32-bit code execution at maximum clock rate. LPC2132 has 6 channels of PWM and 8 channels of 10-Bit A/D converter which are sufficient to implement a single-phase full-bridge inverter.

#### 2.2.3 TMS320F28335 DSP

TMS320F28335 is a high-performance static CMOS (Complementary Metal-Oxide Semiconductor) technology with speed up to 6.67ns cycle time. The total harmonic distortion

(THD) is inversely proportional to the switching frequency of the rectifier/inverter-bridge, which means using a high-speed DSP to implement active rectifier with PFC or GCI, which has the features of high reliability and power quality.

Enhanced control peripherals include 18 PWM outputs and 16 channel AD converters with 12-Bits resolution and 80ns high speed sampling rate. The most prominent feature of the F28335 DSP is that it has an excellent floating point, built-in coprocessor.

### 2.2.4 Insulated-gate bipolar transistor (IGBT)

An IGBT FF75R12RT4 shown in Figure 2-6 was utilised to build the three-phase rectifier/inverter-bridge; it is 34mm module with fast Trench/Fieldstop IGBT4 and Emitter Controlled 4 diodes, produced by Infineon. The voltage stresses of FF75R12RT4 between collector and emitter is up to 1200V, continuous DC maximum collector current is 75A and maximum repetitive peak collector current is 150A. The maximum turn-on and turn-off delay times are 0.15µs and 0.40µs respectively for inductive loads (MK, 2013-11-05).

Figure 2-6 IGBT FF75R12RT4

### 2.2.5 Voltage and current transducers

TBC50SYH was chosen to measure three-phase rectifier current due to its 50A nominal current rating. The TBC-SYH series high-precision current sensor is a closed loop device based on Hall Effect, with a galvanic isolation between primary and secondary circuit. It has strong antijamming ability and can provide accurate electronic measurement of DC, AC or pulsed currents.

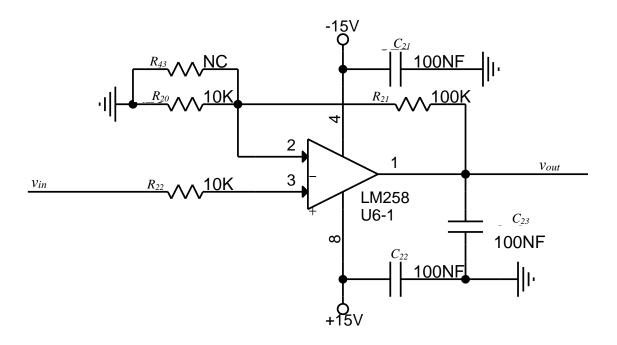

The TLP7820 optically isolated amplifier was used to measure voltage, using a delta-sigma AD converter input circuit and providing an analogue output via a 1 bit D/A and a low pass filter. Figure 2-7 shows sampling of an input voltage.

Figure 2-7 Sampling circuit of input voltage

The TLP7820 device, which is shown in Figure 2-8, can detect small current and voltage fluctuations with high-precision. It offers a common-mode transient immunity of  $15kV/\mu s$  minimum, enabling stable operation in electrically noisy environments.

Figure 2-8 TLP7820 device

Figure 2- 9 Linear relationship between input and output of TLP7820

According to the datasheet of the TLP7820, the analogue input voltage is limited between -300 mV +300 mV as shown in Figure 2-9. Assuming a maximum input the AC peak voltage of  $300 \times \sqrt{2}$ V, this must then be attenuated to 300mV. According to Figure 2-7, the gains  $G_s$  of sampling input voltage can be obtained in the following equation:

$$G_S = \frac{R_2}{R_{1a} + R_{1b} + R_{1c} + R_2} = 7.7459 \times 10^{-4}$$

(2 - 1)

Because the TLP7820 output signal is limited -300mV and +300mV without an amplifier, an additional stage of amplification with a gain of 10 was added between the output and sampling input, as shown in Figure 2-10.

Figure 2- 10 Sampling Gain

### 2.3 Software environment

### 2.3.1 MATLAB/Simulink

Simulink is a user friendly block diagram environment for simulation and Model-Based design, supporting simulation, automatic code generation, and continuous test and verification of embedded systems.

Simulink provides a graphical editor, customizable block libraries, and solvers for modelling and simulating dynamic systems. It is integrated with MATLAB, enabling incorporation of MATLAB algorithms into models and exportation of simulation results to MATLAB for further analysis.

### 2.3.2 Keil uVision

The MDK-ARM is a complete IDE for Cortex-M, Cortex-R4, ARM7 and ARM9 processor based devices. It is specifically designed for microcontroller applications with easy to use and

powerfully adequate for most embedded applications. Therefore, MDK-ARM was chosen to program the central control system using C/C++ language.

### 2.3.3 Code composer studio

Code composer studio (CCS) is an IDE that supports TI's Microcontroller and Embedded Processors portfolio and comprises a suite of tools used to develop and debug embedded applications. CCS has resources to help developers, which can shorten development cycles and reduce development costs and improve development efficiency. The technology of Real-time Exchange Data (RTXD) was developed by TI, and gives designers continuous, real-time visibility into their applications. The bi-directional capability allows developers to access data from the application for real-time visibility, or to simulate data input to the DSP, perhaps before real-time sensor hardware is available.

In Simulink, the accuracy of results of simulation depends on the time step interval (The Math Works 2011). In general, the smaller the time step, the more accurate the simulated results. In the case of variable-step solvers, the solver can automatically determine the time step; in the case of fixed-step solvers, the time step can be specified. Therefore, the results of simulation based on MATLAB/Simulink have some tolerances compared with ideal mathematical models.

### 2.4 Mathematical methods

#### 2.4.1 Clarke's transformation

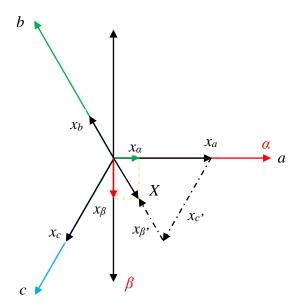

Clarke's Transformation as shown in Figure 2-11. Considering a vector X ( $x_a$ ,  $x_b$  and  $x_c$ ), a-, b- and c- are the component vectors in directions a, b and c, respectively, in the static three-phase system.  $x_\alpha$  and  $x_\beta$  are  $\alpha$ - and b-component vectors of X in the stationary two-phase frame  $\alpha\beta$  respectively. As Figure shows, the vector X in three-phase system can be expressed in stationary two-phase frame.

Figure 2 - 11 Clarke's Transformation

The voltages of a three-phase balanced system can be written as the following mathematical model:

$$\begin{cases} v_{a} = v_{max} \cos \omega t \\ v_{b} = v_{max} \cos \left(\omega t - \frac{2\pi}{3}\right) \\ v_{c} = v_{max} \cos \left(\omega t - \frac{4\pi}{3}\right) \end{cases}$$

(2-2)

Let

$$v_{\alpha} = v_{max} \cos \omega t$$

And the orthogonal variable of  $v_{\alpha}$  be  $v_{\beta}$ , so that:

$$v_{\beta} = v_{max} \sin \omega t$$

Adopting  $v_{\alpha}$  and  $v_{\beta}$  to simplify Equation (2-2) as follows:

$$v_{a} = v_{\alpha}$$

(2 - 2.1)

$$v_{b} = v_{max}(\cos \omega t \cos \frac{2\pi}{3} + \sin \omega t \sin \frac{2\pi}{3})$$

$$= -\frac{1}{2}v_{\alpha} + \frac{\sqrt{3}}{2}v_{\beta} \tag{2-2.2}$$

$$v_c = v_{max}(\cos\omega t\cos\frac{2\pi}{3} - \sin\omega t\sin\frac{2\pi}{3})$$

$$= -\frac{1}{2}v_{\alpha} - \frac{\sqrt{3}}{2}v_{\beta} \tag{2-2.3}$$

Therefore, rearranging  $v_a$ ,  $v_b$  and  $v_c$

where

$$A = \begin{bmatrix} 1 & 0 \\ -1/2 & \sqrt{3}/2 \\ -1/2 & -\sqrt{3}/2 \end{bmatrix}$$

### 2.4.2 Inverter Clarke's transformation

Finding the inverse matrix for the matrix A, then multiplying both sides of Equation (2-3) by the inverse of A results in Equation (2-4) giving  $v_{\alpha}$  and  $v_{\beta}$ .

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -1/2 & -1/2 \\ 0 & \sqrt{3}/2 & -\sqrt{3}/2 \end{bmatrix} \begin{bmatrix} v_{a} \\ v_{b} \\ v_{c} \end{bmatrix}$$

(2 - 4)

where,

$v_{\alpha}, v_{\beta}$  are the stationary orthogonal reference frame quantities.

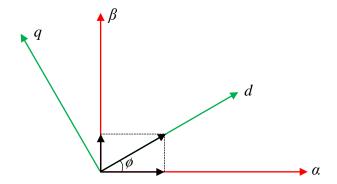

### 2.4.3 Park's transformation

The two-axis stationary orthogonal reference frame quantities are transformed into a d-q rotating reference frame using the Park's transformation as illustrated in Figure 2-12.

Figure 2- 12 Park's transformation

The rotating reference frame d-q quantities can be obtained as follows.

$$\begin{cases} v_d = v_\alpha \cos \emptyset + v_\beta \sin \emptyset \\ v_q = v_\beta \cos \emptyset - v_\alpha \sin \emptyset \end{cases}$$

(2-5)

where,

$v_d$ ,  $v_q$  are the rotating reference frame quantities.

$v_{\alpha}$ ,  $v_{\beta}$  are the stationary orthogonal reference frame quantities.

$\phi$  is the rotational angle.

### 2.4.4 Inverse Park's transformation

Then the Inverse Park's transformation can be expressed as the following equation:

$$\begin{cases} v_{\alpha} = v_{d} \cos \emptyset - v_{q} \sin \emptyset \\ v_{\beta} = v_{q} \cos \emptyset + v_{d} \sin \emptyset \end{cases}$$

(2-6)

where,

$v_d$ ,  $v_q$  are the rotating reference frame quantities.

$v_{\alpha}$ ,  $v_{\beta}$  are the stationary orthogonal reference frame quantities.

$\phi$  is the rotational angle.

### 2.4.5 P-Q theory

The voltages of a three-phase balanced system can be written as the following mathematical model:

$$\begin{cases} v_{sa} = A_m \cos \omega t \\ v_{sb} = A_m \cos \left(\omega t - \frac{2\pi}{3}\right) \\ v_{sc} = A_m \cos \left(\omega t - \frac{4\pi}{3}\right) \end{cases}$$

(2-7)

Through the d-q coordinate transformation, the voltage of a three-phase system in the d-q rotating frame system can be expressed as:

$$\begin{cases} v_d = A_m \\ v_q = 0 \end{cases} \tag{2-8}$$

According to the instantaneous power of P-Q theory, the three-phase active power P and reactive power Q can be written in the stationary frame system  $\alpha\beta$  as

$$\begin{bmatrix} P \\ Q \end{bmatrix} = \begin{bmatrix} v_{\alpha} & v_{\beta} \\ v_{\beta} & -v_{\alpha} \end{bmatrix} \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} \tag{2-9}$$

where  $v_{\alpha}$ ,  $v_{\beta}$  and  $i_{\alpha}$ ,  $i_{\beta}$  are mutually orthogonal pair of voltages and currents respectively.

Through Park's transformation, Equation (2-9) can be expressed as follows:

$$\begin{cases} P = v_d i_d + v_d i_q cos\omega t (sin\omega t - cos\omega t) \\ Q = -v_d i_q \end{cases}$$

(2-10)

In Equation (2-10), as  $i_q$  approaches 0 then the reactive power component approaches 0 and only the active power remains, i.e. the term  $v_d i_d$ . Through analysing the above equation, the reactive power Q of the power grid can be controlled by adjusting the instantaneous quadrature component of current  $i_q$  in the d-q rotating frame.

# 2.5 Summary

In this chapter, the experimental environment, including hardware, software and programming IDE, are briefly introduced. Mathematical tools, particularly Park's, Clarke's transformation and P-Q theory, are addressed as well. These tools are widely employed in power electronic control algorithm development.

# **Chapter 3 Phase-Locked Loop**

## 3.1 Introduction

PLLs are common signal processing methods. They are widely used in applications such as measurement, coherent demodulation, time synchronisation, frequency synthesis, and other signal processing fields. There are a number of types of PLL depending on the implementation technology, including analogue PLL (APLL), digital PLL (DPLL), synchronous frame PLL (SFPLL) and soft PLL (SPLL). In the development of virtual radio technology, SPLL has been used widely (Liu, et al., 2007). The basic principle of SPLL is similar to that of conventional PLL, but differs significantly in the mathematical model, parameter design and implementation modalities (Bhardwaj, 2013) (Guo, et al., 2011).

The frequency, phase angle and amplitude of the AC voltage on the electricity grid are critical parameters for a GCI, employed to inject AC power to the grid, to ensure the inverter system operates properly and does not cause grid transients. In order to generate the reference control signals for the PWM control of the inverter switches, accurate detection of the phase angle of the electrical quantities on the grid is essential.

A few topologies of PLL for GCIs have been implemented in industrial applications. The sine and cosine of the phase angle are key parameters for a GCI; conventional methods yield those parameters by firstly obtaining phase angle from the power grid voltage, then through a series triangular computations. Actually, because the grid voltage is a sine signal, obtaining the grid voltage phase angle is unnecessary if a pair of orthogonal signals from a sampling of the sine signal can be obtained. The SOGI can generate a pair of orthogonal signals, therefore a SOGIPLL, with a strong anti-interference PLL algorithm, has been introduced to achieve phase synchronisation with the grid. This technique has been analysed in detail in the analogue

continuous-time domain (Rodriguez, et al., 2009) and the implementation in the digital discrete-time domain is described in this chapter. Finally the results of simulation are presented.

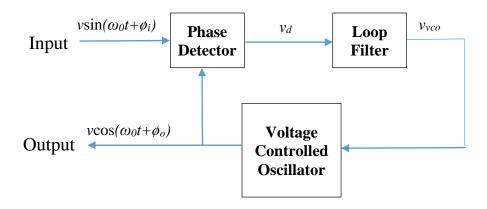

### 3.2 Generic PLL

Figure 3-1 shows the functional block diagram of a generic PLL, where  $\phi_i$  and  $\phi_o$  are the relative phase angles of the input and output voltage signals  $v_i$  and  $v_o$ . The Phase Detector multiplies the input and output signals and produces a voltage  $v_d$  proportional to the phase difference between the input frequency with feedback frequency output, which contains a second harmonic term that need to be removed by the Loop Filter, which is a low-pass filter. The Loop Filter outputs voltage  $v_{vco}$  which is proportional to the phase difference  $\phi_i - \phi_o$  and employed to control the Voltage Controlled Oscillator (VCO).

Figure 3-1 Diagram of generic PLL

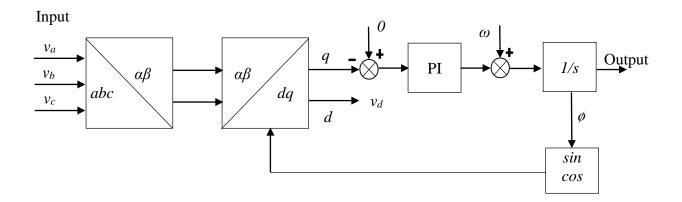

A conventional linearised SFPLL block diagram is illustrated in Figure 3-2, which is widely employed in three-phase GCI applications. The instantaneous phase angle  $\phi$  is detected by synchronising the d-q rotating reference frame with the three-phase electricity grid. When the phase angle is locked to the phase angle of grid voltage vector, the output quadrature component should be 0 and the direct component indicates the grid voltage amplitude.

Figure 3- 2 Linearised conventional SFPLL block diagram

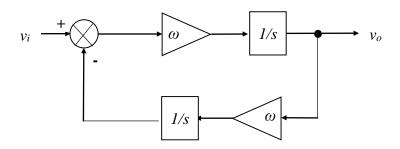

## 3.3 SOGISPLL mathematical model

Figures 3-3 and 3-4 illustrate block diagrams of both open-loop and close-loop implementations of a SOGI, respectively (Fan & Liu, 2015).

Figure 3-3 Open-loop system of SOGI

Figure 3- 4 Close-loop system of SOGI

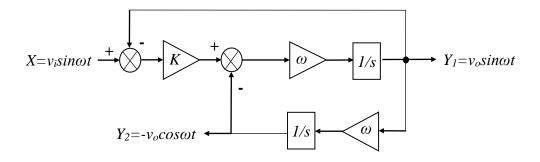

According to the Figures above, let X represent the input signal  $v_i sin\omega t$ , let  $Y_1$  represent the output signal  $v_o sin\omega t$  and  $Y_2$  represent the output signal  $-v_o cos\omega t$ , then the mathematical model of the close-loop system in the Laplace domain can be expressed as:

$$\begin{cases} Y_1 = \frac{(K(X - Y_1) - Y_2)\omega}{s} \\ Y_2 = \frac{Y_1\omega}{s} \end{cases}$$

(3 - 1)

where,

*K* is the gain which affects the speed of response and the bandwidth of the close-loop system,

$\omega$  is the signal frequency in radians, and

$\frac{1}{s}$  is the integrator in Laplace domain.

Substituting  $\frac{Y_1\omega}{s}$  for  $Y_2$  and rearranging Equation (3-1) yields:

$$\begin{cases} Y_1 = \frac{K\omega s X}{s^2 + K\omega s + \omega^2} \\ Y_2 = \frac{K\omega s X}{s^2 + K\omega s + \omega^2} \cdot \frac{\omega}{s} \end{cases}$$

(3-2)

So the transfer function of the close-loop system can be obtained as:

$$\begin{cases} H_{s1} = \frac{Y_1}{X} = \frac{K\omega s}{s^2 + K\omega s + \omega^2} \\ H_{s2} = \frac{Y_2}{X} = \frac{K\omega^2}{s^2 + K\omega s + \omega^2} \end{cases}$$

(3-3)

Converting the denominators to the standard second order form:

$$s^2 + 2\zeta\omega s + \omega^2 \tag{3-4}$$

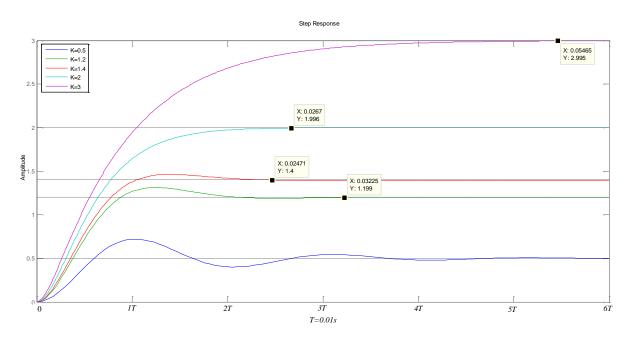

where,  $\zeta$  is the damping factor (typically  $\zeta=1/\sqrt{2}=0.707$ ), so in the term of denominator of Equation (3-3),  $K=2\zeta=1.414$  and the frequency of the electricity grid is 50 Hz, which means  $\omega=2\pi50$  rad/s.

Figure 3-5 illustrates the step responses of the system with the gain of K=0.5, 1.2, 1.414, 2 and 3 respectively. These responses show that the system reaches steady state conditions, and the shortest time is 0.0247s when the gain  $K=2\zeta=\sqrt{2}$  (i.e.  $\zeta=\frac{1}{\sqrt{2}}$ ), as the response in red on the graph below.

Figure 3- 5 Step responses of a closed-loop SOGIPLL in continuous-time

Equation (3-3) is the transfer function of the close-loop system in continuous-time in the Laplace domain. The equivalent discrete-time transfer function is required to implement the second order integrator in a digital signal system. There are a number of methods that can be employed to obtain the discrete-time approximation of a continuous-time transfer function, such as Forward Difference, Backward Difference, Tustin's Approximation and Bilinear Transformation. (Ogata, 1995).

Tustin's approximation, also known as Euler's method or Trapezoidal Approximation, (Ciobotaru, et al., 2006) is a common method and is demonstrated below using the substitution  $\frac{2}{T}\frac{z-1}{z+1}$  to replace the Laplace operator s.

$$H_{s1} = \frac{Y_1}{X} = \frac{K\omega s}{s + K\omega s + \omega^2} = \frac{444.2208s}{s^2 + 444.2208s + 98696.044}$$

Substituting  $\frac{2}{T} \frac{z-1}{z+1}$  for the Laplace operator for s and sampling time 2e-5s for T, results in

$$H_{z1} = \frac{444.2208 \frac{2}{2 \times 10^{-5}} \frac{z - 1}{z + 1}}{\left(\frac{2}{2 \times 10^{-5}} \frac{z - 1}{z + 1}\right)^2 + 444.2208 \frac{2}{2 \times 10^{-5}} \frac{z - 1}{z + 1} + 98696.044}$$

This result simplifies to

$$H_{z1} = \frac{0.004423z^2 - 0.004423}{z^2 + 1.991z + 0.9912} \tag{3-5}$$

$$H_{s2} = \frac{Y_2}{X} = \frac{K\omega^2}{s^2 + K\omega s + \omega^2} = \frac{139556.21}{s^2 + 444.2208s + 98696.044}$$

Substituting the Laplace operator s with  $\frac{2}{T}\frac{Z-1}{Z+1}$  and sampling time T with 2e-5s

$$H_{z2} = \frac{139556.21}{\left(\frac{2}{2 \times 10^{-5}} \frac{z-1}{z+1}\right)^2 + 444.2208 \frac{2}{2 \times 10^{-5}} \frac{z-1}{z+1} + 98696.044}$$

On rearrangement this becomes

$$H_{z2} = \frac{1.389 \times 10^{-5} z^2 + 2.779 \times 10^{-5} z + 1.389 \times 10^{-5}}{z^2 + 1.991z + 0.9912}$$

(3 - 6)

MATLAB's c2d command can also be utilised to convert continuous to discrete transfer function as in the following example.

```

>> W=2*pi*50;

>> K=1.414;

>> H1=tf([K*W 0],[1 K*W W*W])

H1 =

444.2 s

s^2 + 444.2 s + 9.87e04

Continuous-time transfer function.

>> HD1=c2d(H1,2e-5,'tustin')

HD1 =

0.004423 z^2 - 0.004423

z^2 - 1.991 z + 0.9912

Sample time: 2e-05 seconds

Discrete-time transfer function.

>> W=2*pi*50;

>> K=1.414;

>> H2=tf(K*W*W,[1 K*W W*W])

H2 =

1.396e05

s^2 + 444.2 s + 9.87e04

Continuous-time transfer function.

>> HD2=c2d(H2,2e-5,'tustin')

HD2 =

1.389e-05 z^2 + 2.779e-05 z + 1.389e-05

_____

z^2 - 1.991 z + 0.9912

Sample time: 2e-05 seconds

Discrete-time transfer function.

```

The MATLAB results and the results produces by Tustin's Approximation are the same.

## 3.4 Discrete Implementation of SOGIPLL

Equations (3-5) and (3-6) show that the SOGIPLL system response functions are second-order digital filters with feedback. Hence, they can be achieved using an infinite impulse response (IIR) digital filter. The standard form of a digital second order IIR filter is shown below:

$$H_d(Z) = \frac{b_0 + b_1 z^{-1} + b_2 z^{-2}}{a_0 + a_1 z^{-1} + a_2 z^{-2}}$$

where  $b_0$ ,  $b_1$  and  $b_2$  are feed-forward coefficients

$a_0$ ,  $a_1$  and  $a_2$  are feed-back coefficients

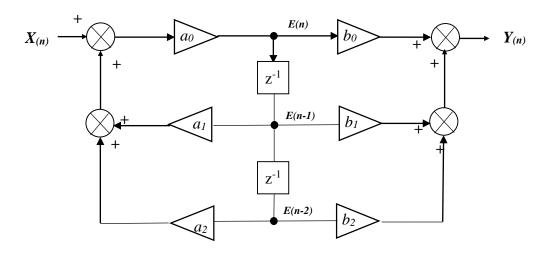

Figure 3-6 shows a general block diagram of the digital second order IIR filter in Direct Form II structure.

Figure 3- 6 Direct Form II structure for IIR filter

where the  $Z^{-1}$  blocks represent a single sample delay and the nodes  $E_{(n)}$ ,  $E_{(n-1)}$  and  $E_{(n-2)}$  represent memory for temporary storage during the calculations.

The Equations of the discrete transfer function, (3-5) and (3-6), can be written as the relationship between instantaneous input and output as follows:

$$H_{z1} = \frac{v_{o(n)}}{v_{i(n)}} = \frac{Y_{1(n)}}{X_{(n)}} = \frac{0.004423z^2 - 0.004423}{z^2 + 1.991z + 0.9912}$$

(3 - 7)

$$H_{z2} = \frac{v_{o(n)}}{v_{i(n)}} = \frac{Y_{2(n)}}{X_{(n)}} = \frac{1.389z + 2.779 \times 10^{-5}z + 1.389 \times 10^{-5}}{Z^2 + 1.991z + 0.9912}$$

(3 - 8)

where  $v_{i(n)}$  is the system discrete input and  $v_{o(n)}$  is the system discrete output.

Multiplying the numerator and denominator by  $z^{-2}$  and solving for instantaneous output  $Y_{I(n)}$ . For Equation (3-7) this gives.

$$(1+1.991z^{-1}+0.9912z^{-2})Y_{I(n)} = (0.004423-0.4423z^{-2})X_{(n)}$$

Which yields

$$Y_{I(n)} = 0.004423X_{(n)} - 0.4423z^{-2}X_{(n)} - 1.991Z^{-1}Y_{I(n)} - 0.9912z^{-2}Y_{I(n)}$$

According to  $X_{(n)}z^{-k} = X_{(n-k)}$  and  $Y_{1(n)}z^{-k} = Y_{2(n-k)}$ , rearranging the equation above gives

$$Y_{I(n)} = 0.004423X_{(n)} - 0.4423X_{(n-2)} - 1.991Y_{I(n-1)} - 0.9912Y_{I(n-2)}$$

(3-9)

Now for Equation (3-9), multiplying the numerator and denominator by  $z^{-2}$  and solving for instantaneous output  $Y_{2(n)}$  gives.

$$(1+1.991z^{-1}+0.9912z^{-2})Y_{2(n)} = (1.389x10^{-5}+2.779x10^{-5}z^{-1}+1.389x10^{-5}z^{-2})X_{(n)}$$

Substituting  $X_{(n)}z^{-k} = X_{(n-k)}$  and  $Y_{2(n)}z^{-k} = Y_{2(n-k)}$ , and rearranging gives

$$Y_{2(n)} = 1.389 \times 10^{-5} X_{(n)} + 2.779 \times 10^{-5} X_{(n-1)} + 1.389 \times 10^{-5} X_{(n-2)} - 1.991 Y_{2(n-1)} - 0.9912 Y_{2(n-2)}$$

(3-10)

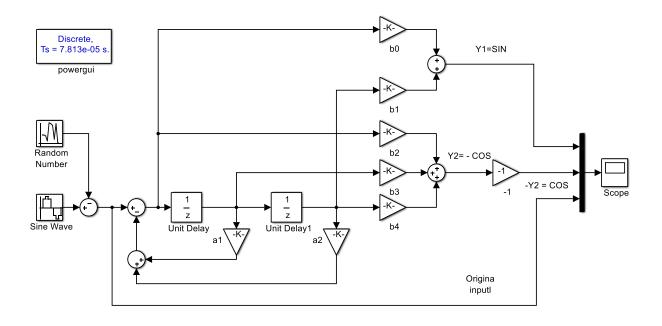

### 3.5 Simulation

The Simulink model created by utilising MATLAB/Simulink according to Equations (3-9) and (3-10) is illustrated in Figure 3-7. A random white noise generator is added at the input terminal to test the stability and anti-interference capability of the system. In a practical system, the

sampling accuracy of the analogue to digital signal converter is affected by noise and/or system drift.

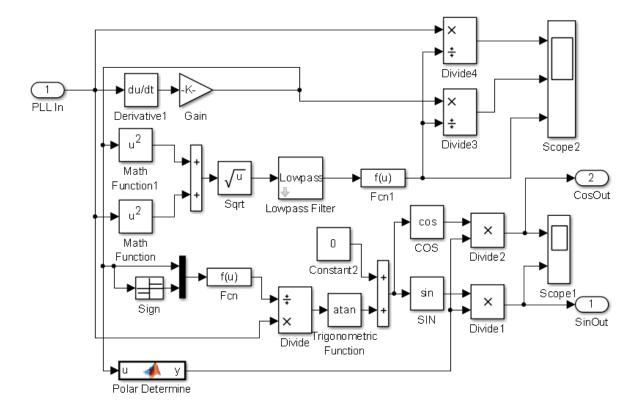

Figure 3-7 Simulink model of SOGIPLL

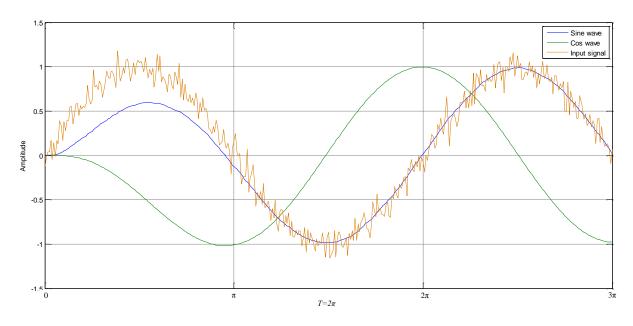

Figure 3-8 Comparison between input with white noises and PLL output

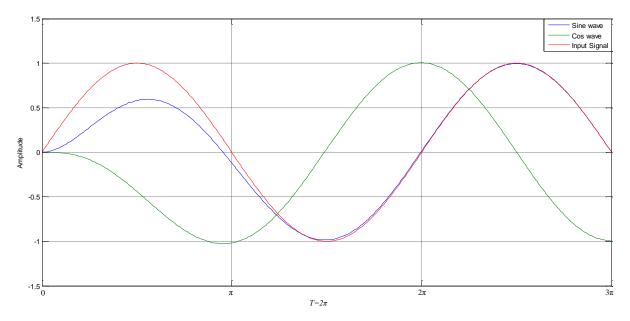

Figure 3-9 Comparison of original input and PLL output

Figure 3-8 shows that the output of the SOGIPLL has anti-interference performance when random white noise is added to an input signal with 50 Hz frequency. Additionally, Figure 3-9 shows the sine (blue line) and cosine (green line) generated by the SOGIPLL follows the original input signal (red line) after one periods, the difference between the output (blue line) and the input (red line) wave has decreased to negligible levels.

# 3.6 Summary

The simulation results demonstrate that SOGI orthogonal output signals with anti-interference performance can be employed to implement PLL in a GCIS. In addition, SOGI only requires one input signal, which means the model can be applied in both single-phase and three-phase GCIs.

# **Chapter 4 AC to DC Rectifier**

### 4.1 Introduction

A Three-phase SVPWM rectifier has attractive characteristics including controllable DC output voltage, low THD, high power factor for the grid current (Zheng, et al., 2010), and bidirectional power flow, which are the major features considered in this thesis.

Rapid growth of renewable power generation in the past decade has certainly been facilitated advanced inverter technology development, which plays a key role in interfacing renewable power generators with the power grid. The most popular three-phase inverter circuit consists of six IGBT switches in a full-bridge configuration, because IGBT has relative higher voltage and current rating. The single-phase inverter circuit is formed by four IGBT switches in a full-bridge.

The full-bridge topology composed of IGBTs or MOSFETs not only utilities to inverter DC voltage into power grid, it also can implement an active controllable rectifier.

Because each switching devices in full-bridge circuit is equipped with an anti-parallel, flywheel diode to protect the device if the load is inductive, as all the switching devices without PWM control signals the full-bridge circuit could be operated in the uncontrollable rectifier mode, because of each switching device has flywheel diode connected in shunt.

As using PWM signals to control switching devices, then the full-bridge topology could be operated in active controllable rectifier or inverter mode, which depends on different control algorithms.

During off-peak or low-tariff hours for peak-hour or high-tariff hours use, integrating energy storage on the DC bus link to store power from grid has great potential advantage.

Conventional renewable energy GCI interfaces to the power grid with as much renewable generator power output as it can deliver but does not offer RPC, which is normally provided by dedicated local reactive power or is matched by the reactive capability of synchronous generators in large power stations.

For a load centre, it is a general practice to compensate reactive power demand from the load centre at the PCC so as to maintain a statutory voltage at the PCC and the distribution network and minimise the line loss. Large synchronous generators are required to produce reactive power, because transmission lines demand reactive power in addition to that needed at distribution load centres. For a more distributed power generation system, it would be ideal that all generation units share the responsibility of providing reactive power.

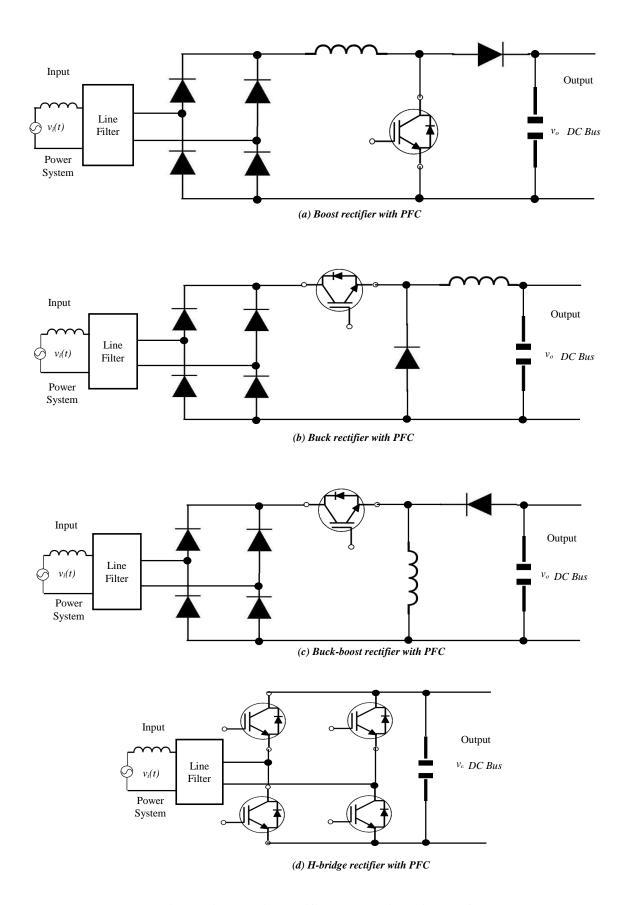

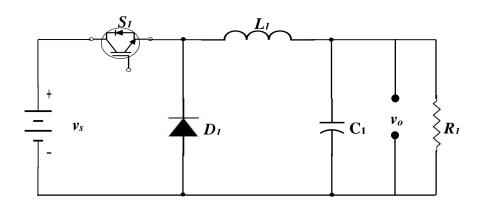

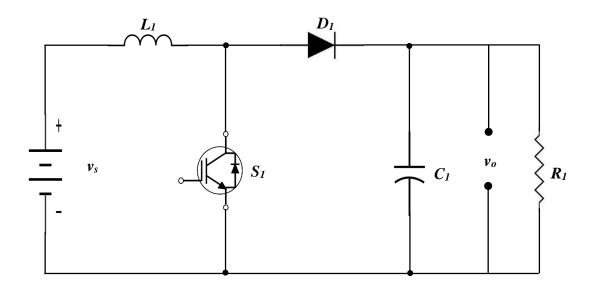

There are a number of topologies presented to implement active rectifiers with PFC, such as the buck rectifier, boost rectifier, buck-boost rectifier, H-bridge converters (Rodriguez, et al., 2016), and Vienna rectifier (Kedjar, et al., 2014; Shaon & Salam, 2014). Figure 4-1 shows the basic rectifier topologies with PFC.

Although all the topologies of single-phase active rectifiers shown in Figure 4-1 can achieve high performance PFC, only Figure 4-1(d) can provide bi-directional power flow for a single-phase system.

Figure 4- 1 Basic rectifier topologies with PFC

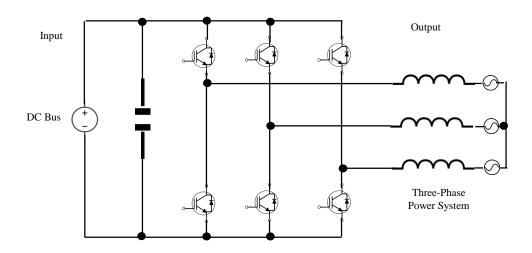

Because the voltage stress of each switching device is only half of the total output voltage, the topology of the Vienna rectifier shown in Figure 4-2 is the most attractive (Shaon & Salam, 2014) in the application of large power rectifiers.

Figure 4- 2 Topology of Vienna rectifier

In terms of control measures, there are many control techniques presented in literature; examples include PWM, sinusoidal PWM (SPWM), Hysteresis PWM (HPWM), SVPWM, and Fuzzy PWM (FPWM). Although the switching losses of the SPWM can be reduced by means of modifying the carrier signal, it results in greater harmonic distortion, which causes poor power factor (Ting, et al., 2015). The control algorithm of HPWM is simple and has greater dynamic response than the PWM and SVPWM because the PWM ratio is adjusted at each PWM period; on the other hand, it has a higher ripple current (Ting, et al., 2015). The SVPWM has low switching losses and provides superior overall performance and power conversion efficiency (Ahmed & Ali, 2013), and is broadly used to implement active controllable rectifiers with PFC in three-phase systems.

The PWM algorithm is widely used in single-phase, buck, boost, and buck-boost rectifiers, according to the linear relationship between the instantaneous input and output to regulate the ratio of PWM duty.

This chapter presents a SVPWM rectifier algorithm based on three-phase GCI topology to achieve an active rectifier with PFC and presents a novel rectifier algorithm for a single-phase rectifier with PFC, so that an inverter cannot only deliver quantitative active power with quantitative RPC to the grid when it operates as an inverter, but can also implement an active rectifier with PFC.

In the topology of a three-phase inverter shown in Figure 4-3, each of the IGBTs shunts a freewheeling diode in the full-bridge inverter circuit so as to provide a complete circuit loop to protect the IGBTs from being damaged by the reverse current of an inductive load when the IGBTs are switched off. This means the circuit actually can be operated as a conventional uncontrolled rectifier while the voltage source is considered as an electrical load.

Figure 4- 3 Topology of three-phase full-bridge inverter

The disadvantages of a conventional power rectifier utilising passive diodes and capacitors contain AC current distortion and harmonic injection to the power grid. Harmonics are a major factor in determining power quality due to increasing non-linear loads; its impedance changes with the applied voltage in power systems. Harmonics cause problems in power systems and in consumer products, such as voltage distortion at the PCC (Bakar, 2008), capacitors in

equipment overheating, motor vibration, excessive neutral currents and lower power factor (Kale & Ozdemir, 2005), contribute low power conversion efficiency to the system. So improving the power factor, stabilising the rectifier DC output and reducing harmonic distortion has attracted the interest of many researchers (Moungkhum & Subsingha, 2013). Figure 4-3 is similar to Figure 2-1, they can attain bi-directional current flowing high power quality active rectifier or GCI in a three-phase system. Therefore, the following research about three-phase active rectifier is based on this concept.

## 4.2 Mathematical model of three-phase active rectifier

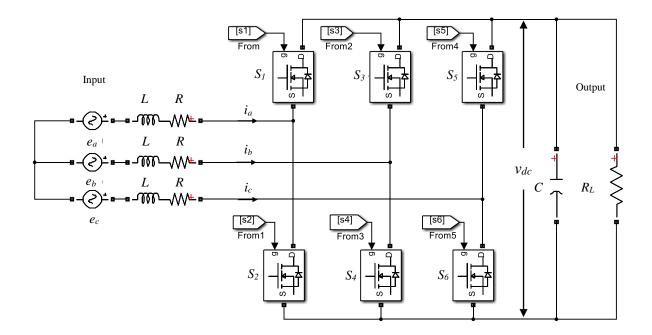

Figure 4-4 illustrates a topology from a MATLAB/Simulink of a three-phase full-bridge active rectifier. The full-bridge topology also can be operated in GCI mode if PWM control signals are changed and the load  $R_L$  in Figure 4-4 is replaced with a DC voltage source, for example DC bus link.

Figure 4- 4 Topology of three-phase full-bridge active rectifier

Hence, the topology illustrated above is able to implement power flowing bi-directionally. The relationships in a dynamic three-phase system of current and voltage can be described in a switched functional mathematical model as follows:

$$\begin{cases} L \frac{di_{a}}{dt} = e_{a} - Ri_{a} - v_{dc} \left( \frac{2S_{u} - S_{v} - S_{w}}{3} \right) \\ L \frac{di_{b}}{dt} = e_{b} - Ri_{b} - v_{dc} \left( \frac{2S_{v} - S_{u} - S_{w}}{3} \right) \\ L \frac{di_{c}}{dt} = e_{c} - Ri_{c} - v_{dc} \left( \frac{2S_{w} - S_{u} - S_{v}}{3} \right) \end{cases}$$

$$(4-1)$$

where

$i_a$ ,  $i_b$  and  $i_c$  are the instantaneous AC currents of phases A, B and C respectively.

$e_a$ ,  $e_b$  and  $e_c$  are the instantaneous voltages of the power grid.

$v_{dc}$  is the voltage of the DC bus.

*R* is the equivalent resistance of the input filter inductors shown in Figure 4-4.

*L* is the inductance of the input filter inductors shown in Figure 4-4.

$S_u$ ,  $S_v$  and  $S_w$  are the switching status of the upper switching devices of each pair switching devices such as  $S_1$  and  $S_2$ ,  $S_3$  and  $S_4$ ,  $S_5$  and  $S_6$  in Figure 4-4 respectively, in which, logic 1 represents that the upper devices are switched on and logic 0 means switched off.

The mathematical model of the three-phase static system is clearly described by Equation (4-1). However, according to Equation (4-1) the design of the control system is a difficult challenge due to the fact that the equation shows the system is a time-variant AC system and the variables to be controlled couple each other making the system complex. Therefore, applying Clarke's and Park's transformation simplifies the process.

Through Clarke's and Park's transformation, Equation (4-1) mathematical model yields the *d-q* rotating reference frame as follows:

$$\begin{cases} L \frac{di_d}{dt} = e_d - Ri_d - v_{dc}S_d + \omega Li_q \\ L \frac{di_q}{dt} = e_q - Ri_q - v_{dc}S_q - \omega Li_d \end{cases}$$

$$(4-2)$$

where

$e_d$  and  $e_q$  are d and q components of the grid three-phase voltage vector  $(e_{dq})$  respectively.

$v_{dc}S_d$  and  $v_{dc}S_q$  are d and q components of the voltage vector of the rectifier at the three-phase grid side respectively.

$i_d$  and  $i_q$  are d and q components of the current vector of the rectifier at the three-phase grid side respectively.

In the d-q rotating reference frame, assuming the  $e_d$  component of the grid three-phase voltage vector falls in the d-direction, the  $e_q$  component is equal to 0. The d and q components in Equation (4-2) still couple each other, so using the feed forward decoupling control method (Milosevic, 2003) with PI control for the current in the d-q frame, then the d and q components of the voltage vector of the rectifier, at the three-phase grid side can be obtained as follows:

$$\begin{cases} v_d = -\left(K_{dp} + \frac{K_{di}}{S}\right)(i_{dr} - i_d) + e_d + \omega L i_q \\ v_q = -\left(K_{qp} + \frac{K_{qi}}{S}\right)(i_{qr} - i_q) + e_q - \omega L i_d \end{cases}$$

(4-3)

where

$K_{dp}$  and  $K_{qp}$  are the proportional gain of the PI compensator.

$K_{di}$  and  $K_{pi}$  are the integrator gain of the PI compensator.

$i_{dr}$  and  $i_{qr}$  are reference current for d and q components of the current vector.

Because at the grid side, d- and q- components of three-phase VSR,  $v_d = v_{dc}S_d$  and  $v_q = v_{dc}S_q$ , so substituting Equation (4-3) into Equation (4-2) to eliminate terms of  $e_d - v_{dc}S_d + \omega Li_q$  and  $e_q - v_{dc}S_q - \omega Li_d$  respectively gives:

$$\begin{cases} L\frac{di_d}{dt} = -Ri_d + \left(K_{dp} + \frac{K_{di}}{S}\right)(i_{dr} - i_d) \\ L\frac{di_q}{dt} = -Ri_q + \left(K_{qp} + \frac{K_{qi}}{S}\right)(i_{qr} - i_q) \end{cases}$$

$$(4-4)$$

## 4.3 Current loop design

The feed forward control as described in Equations (4-3) and (4-4) reveals that the current loop of a three-phase voltage source rectifier has been successfully achieved.

This analysis only focuses on the d-axis quantities of current due to the symmetry between the d and q current quantities, as Equation (4-4) suggests.

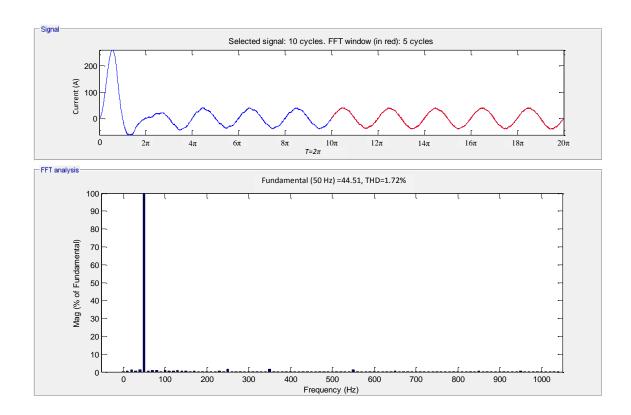

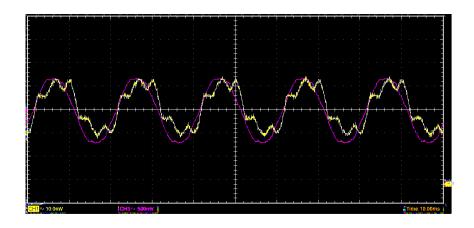

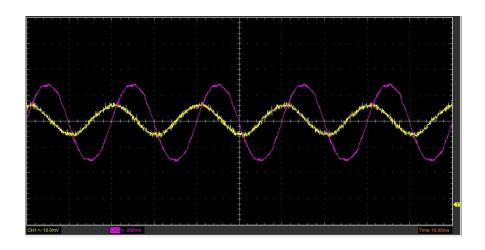

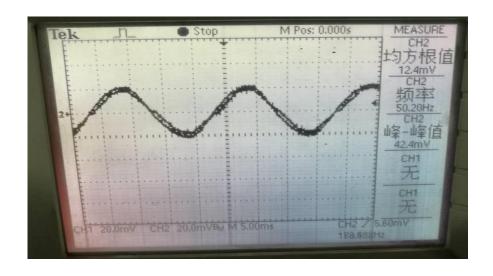

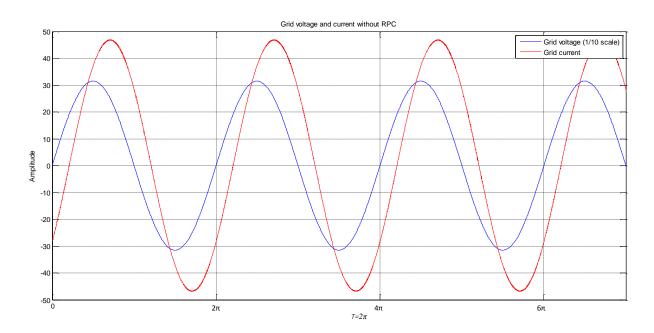

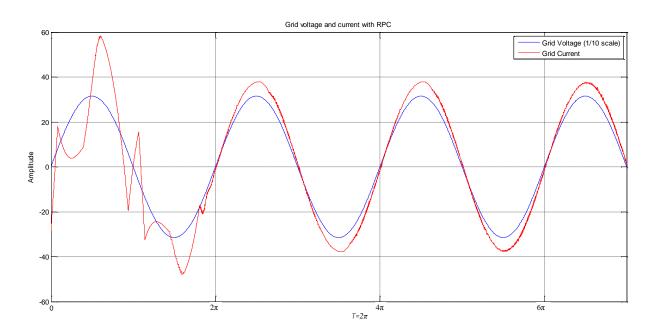

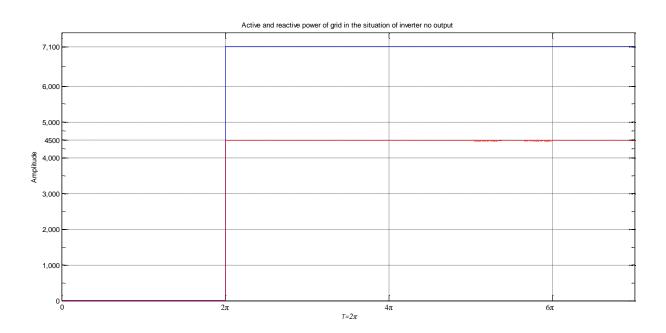

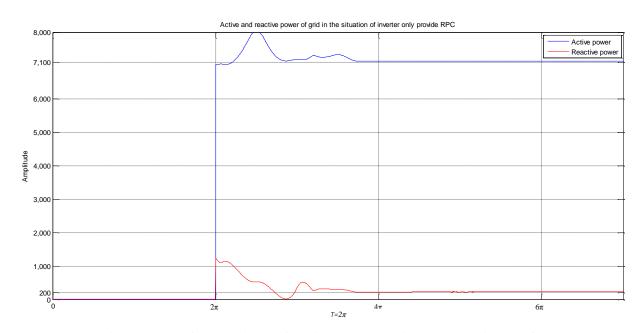

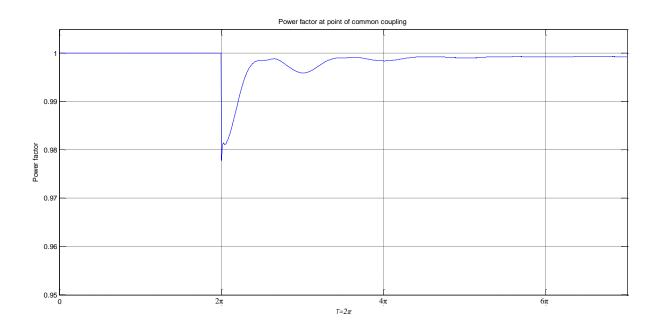

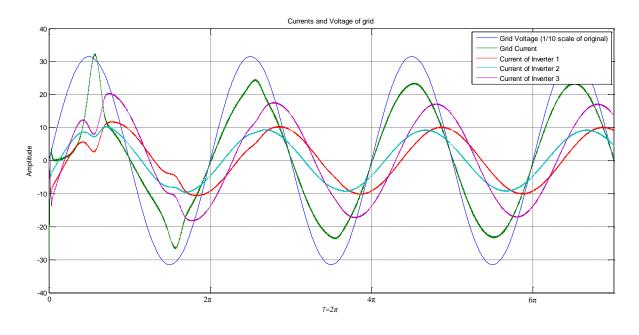

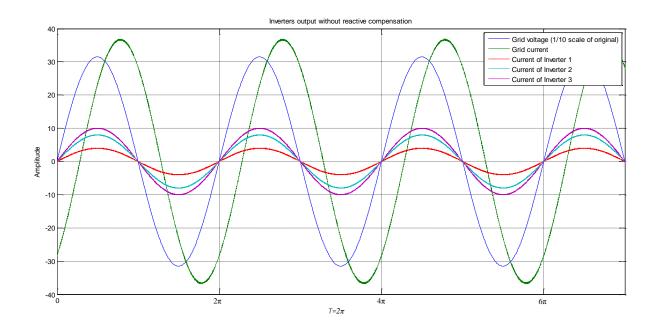

In practical applications, considering some delays from sampling to computation results, in order to enhance system performance and controlled accuracy, it is necessary to add certain delays and gain parameters into a system. The d-component of the current loop control diagram with the perturbation of d-component of the power grid is illustrated in Figure 4-5.